# 集積回路開発40年の歩みでは関係に対し

ADC, アナ・デジ混載SoC, ミリ波CMOS技術を中心として

### 松澤 昭

(株)テックイデア 代表取締役 東京工業大学 名誉教授

### 講演内容

- ・はじめに

- ADCの基本機能と変換アーキテクチャ

- ビデオ用ADCの黎明期 -- バイポーラADCの時代--

- バイCMOSの時代

- CMOSの時代

- ローパワー技術

- CMOS OPアンプの時代 --パイプライン型ADC--

- ダイナミックCMOSアナログの時代 --SAR ADCの革新--

- SoC:システム集積の時代

- 60GHz ミリ波トランシーバの開発

- 教育活動

- まとめ

# はじめに

Pursuing Excellence

### 2022 IEEE Donald O. Pederson Award の受賞

### デジタルビデオ機器用システムLSIに向けた 低電力A/D変換器開発の先駆的な貢献

- 1. デジタルTV・ビデオシステム実現のためのバイポーラADCの開発

- 2. 超低電力CMOS ADCの開発とローパワーエレクトロニクスの振興

- 3. 低電力超高速ADCの開発とアナログ・デジタル混載システムLSIの開発

- 4. ミリ波CMOSトランシーバの開発

IEEE Donald O. Pederson Award in Solid-State CircuitsはIEEEのTechnical Field Awardの一つで、集積回路分野における社会への貢献、技術進歩への貢献、専門的なリーダーシップが顕著な個人、または3人までのチームに授与されるものである。1988年創設のIEEE Solid-State Circuits Award を継承し、2005年に現在の名前に改名された。

### 講演の趣旨

- ・ 半導体(集積回路)は全ての機器の基盤として重要

- 集積回路が実現して初めて機器の小型化、低コスト化、高信 頼化, 高性能化が図れる

- デジタルAV機器, 通信機器, センシングではアナログ信号を デジタル信号に変換するA/D変換器(ADC)が不可欠

- しかしながらアナログ技術をベースとするADCはロジック回 路のように回路が決まっておらず、システム仕様やデバイス に応じた特別な設計技術開発を必要とした

- テレビ・ビデオなどの映像機器の開発と、それに使用する集 積回路の開発は日本が技術と市場をリードしてきた分野

- 講演では、ADCやアナ・デジ混載SoC、ミリ波CMOS技術の 開発における集積回路技術40年の歩みを示す

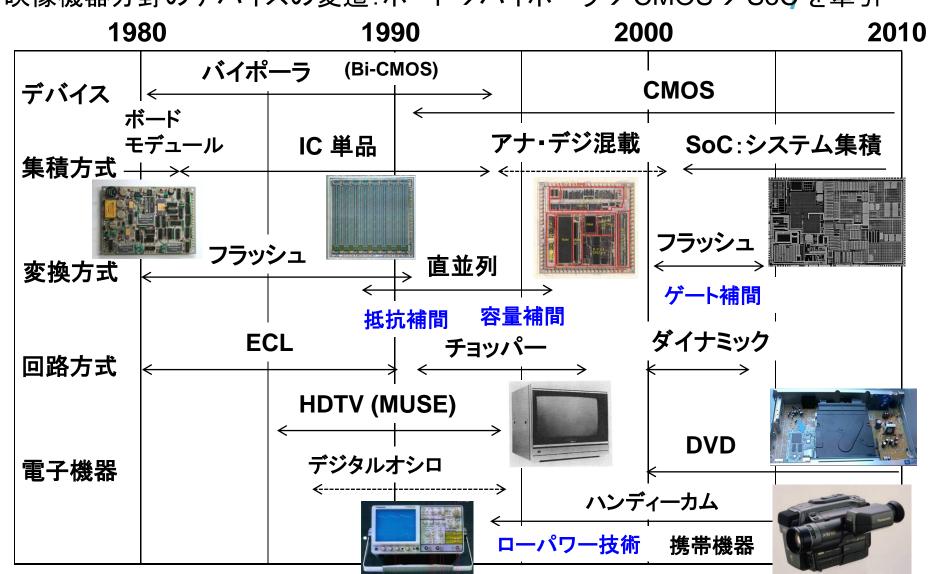

### 集積回路・ADCと電子機器の開発推移

## ADCの基本機能と変換アーキテクチャ

ADCは機器のデジタル化に不可欠な集積回路であるが、アナログ技術をベースにしているため理解が難しい技術である。 用途に応じて要求仕様が異なり、またこれに応じて変換アーキテクチャが異なることも理解を困難にしている。

ここではADCの基本機能と基本A/D変換アーキテクチャを示す。

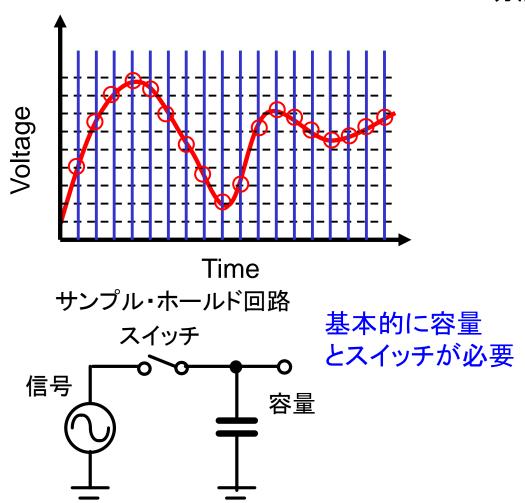

### ADCの基本機能

#### サンプリング

量子化

Pursuing Excellence

決まったタイミングで入力信号を抜き取る

分解能に応じた2進整数値に変換する

2020.12.11

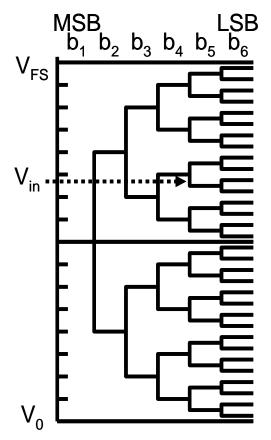

2進探索が基本 Binary Code

**Binary Code**

A. Matsuzawa

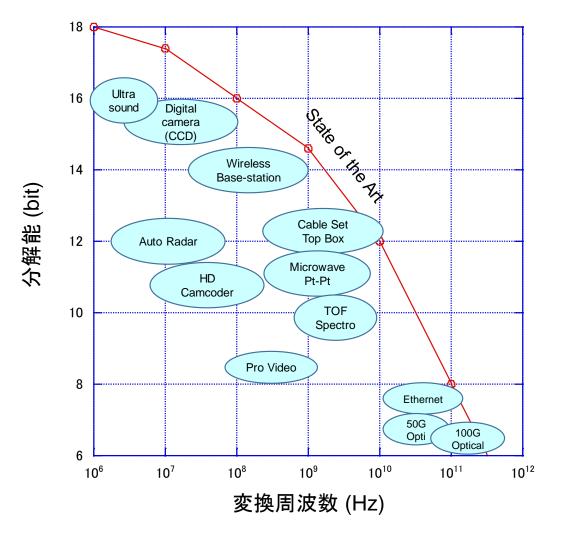

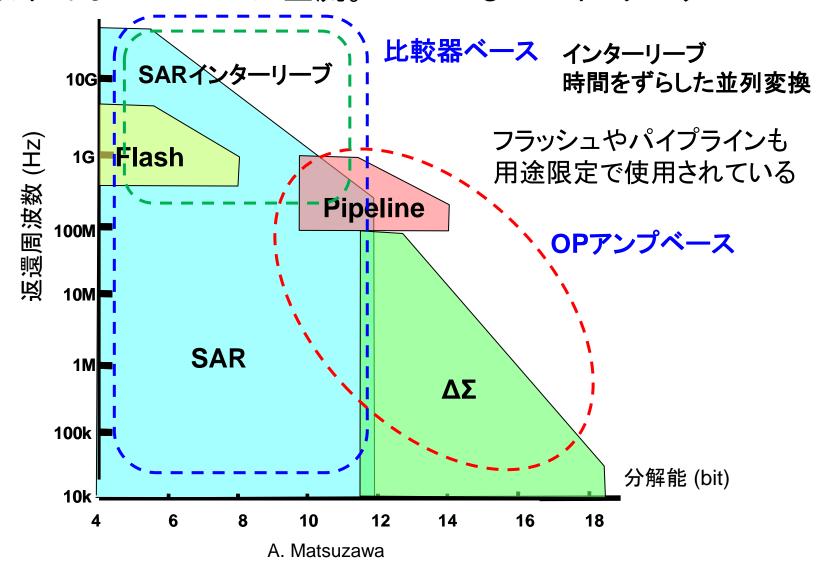

### 変換周波数 • 分解能 • 用途

用途に応じて変換周波数と分解能が異なる これら2つはトレードオフの関係がある

A. Matsuzawa

### ADC の変換方式

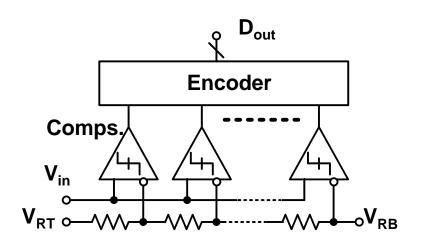

Flash, SAR, パイプライン, ΔΣが主要なアーキテクチャである

Pursuing Excellence

(a) 並列 (フラッシュ)

(b) 逐次比較 (SAR)

2020.12.11 A. Matsuzawa

### 基本的な変換動作

エレメント数、クロック数により基本的に3つの変換手段がある

Pursuing Excellence

#### (a) 並列 (フラッシュ)

#### (b) 逐次比較 (SAR)

#### (c) パイプライン

回路規模大 超高速 回路規模最小 低速(Nクロック必要) S/H回路必要

| $n \approx 2^N$ | 1 | $_{2}^{n}$ | $pprox N_{f 3}$ | 4 |

|-----------------|---|------------|-----------------|---|

| 15              | 1 | 1          | 1               | 1 |

| 14              |   |            |                 | 0 |

| 13              |   |            | 0               | 1 |

| 12              |   |            |                 | 0 |

| 11              | ' | 0          | 1               | 1 |

| 10              |   |            |                 | 0 |

| 9               |   |            | 0               | 1 |

| 8               |   |            |                 | 0 |

| 7               | 0 | 1          | 1               | 1 |

| 6               |   |            |                 | 0 |

| 5               |   |            | 0               | 1 |

| 4               |   |            |                 | 0 |

| 3               |   | 0          | 1               | 1 |

| 2               |   |            |                 | 0 |

| 1               |   |            | 0               | 1 |

| 0               |   |            |                 | 0 |

回路規模小 高速(見かけ上1クロック) S/H+OPアンプ必要

$n \approx N$ n:エレメント数 1\_1 2\_1 1\_2 3 1 2 2 13 4 1 3\_2 23 1\_4 4\_2 3 3 2\_4 43 3\_4 4\_4 時間(クロック)

1クロック

電圧

N クロック

1 クロックのスループット (Nクロックかかるが、、、)

2020.12.11 A. Matsuzawa

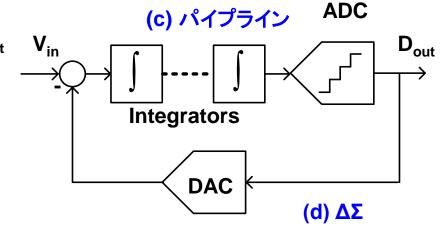

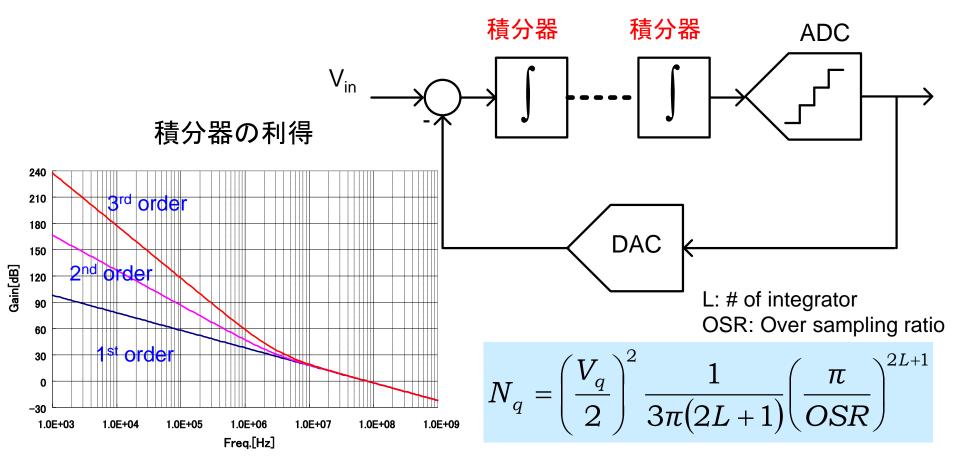

### ΔΣ ADC

積分器は低周波領域で超高ゲインアンプとして働く Pusuing Excellence 負帰還回路に用いると低周波で量子化ノイズを大きく抑制し 高SNRを実現する。高いSNR(>80dB)は $\Delta\Sigma$ ADCしか実現できない

2020.12.11 A. Matsuzawa

### ADCの変換方式と使用領域

12bit以上の分解能ではΔΣ型ADC Pursuing それ以下ではSAR ADCが主流。64GS/sもSARインターリーブ

### ビデオ用ADCの黎明期

### バイポーラADCの時代

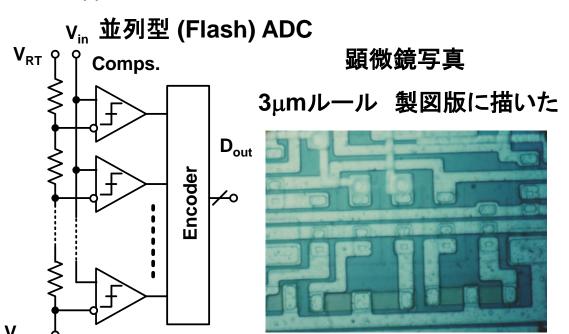

1970年代後半から1980年代におけるアナログ回路に使用できるデバイスはほとんどバイポーラであり、MOSは性能が悪すぎて使用できなかった。ただしバイポーラはADCに不可欠なスイッチと容量が使えなかったため並列型(Flash)に限定された

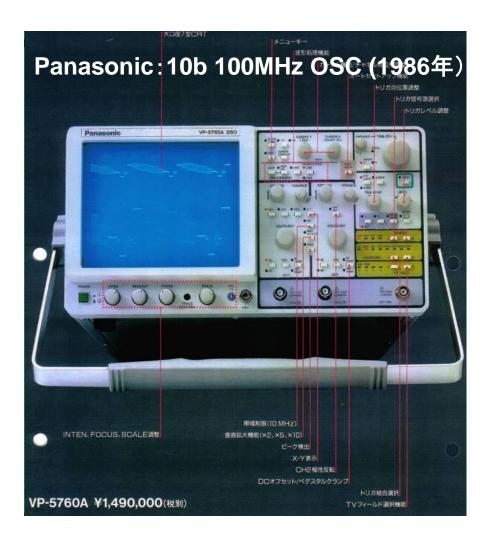

1970年代の終わりから始まったHDTV開発にはビデオ用ADCが必要だったが 当時はIC化された10ビットビデオ用ADCや、HDTVカメラ信号を変換可能なADC は存在しなかった。IC化されたHDTV用のADCはバイポーラ技術が用いられた。 この開発は初期のHDTV開発には貢献したが、市場が立ち上がらなかったので 実際には電子計測器・デジタルオシロなどに使用された。

### デジタルビデオ技術の開発開始

1978年に松下電器に入社し、1979年に中央研究所に配属された。 1978年に松下電器は総力を結集し6時間録画のVHSビデオの開発に成功。 以後ビデオ関連の売り上げは1兆円規模に達し、大黒柱に成長。

ビデオ機器はアナログ技術の粋と言うべきものであったが、 次のデジタルTV・ビデオの開発に向けての研究が開始された。

1979年 中央研究所の配属同期と

Panasonic VHS Video NV-6000, 1979

**Pursuing Excellence**

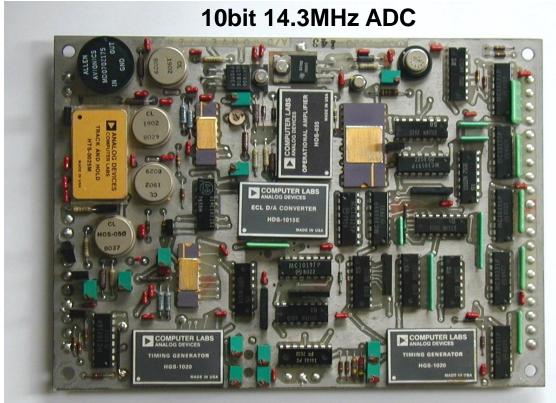

### 当時のビデオ用A/D変換器

TV・ビデオのデジタル化の大きな課題はA/D変換器であった。 当時のビデオ用10bit A/D変換器はボードであり、集積回路化されていなかった。 非常に高価で、消費電力が大きく民生品はおろか、業務用にも使用できなかった。 私の使命はADCを開発し、各種デジタルTV・ビデオ機器を実現することであった。

1979年当時

100万円 !! 20W

**Analog Devices Inc.**

### 日本初のビデオ用 8b ADCの開発

初めての仕事で国産初のビデオ用8b ADCの開発に成功 Pursuing Excellence 当時、唯一TRW社がビデオ用8ビットADCを販売。消費電力をこの1/3に下げた

このADCは横河電機やアドバンテストの電子計測機器用として20年以上販売された。

Bipolar (3um) 8b, 30MS/s, 0.7W 1981年

### 消費電力と面積の低減方法

バイポーラADCはサンプル・ホールドが使用できなかったのでサンプリング動作はラッチ回路で代用された。アーキテクチャはフラッシュに限られた。

この当時はロジックLSIもCMOSではなくNMOSが用いられた。 CMOSが用いられるのは1980年代の後半である。

回路はメインフレームコンピュータ用の ECL (Emitter Coupled Logic)と共通だが ミスマッチ電圧が0.2mV以下が要求される のでTV・ビデオ用ICに用いられるアナログ 用のデバイスが使用された。

バイポーラCMLロジックは定常電流が流れるので、低電力化のためには縦積み段数を増やすことが有効であった。

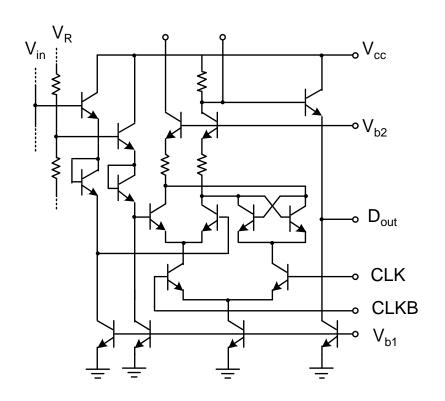

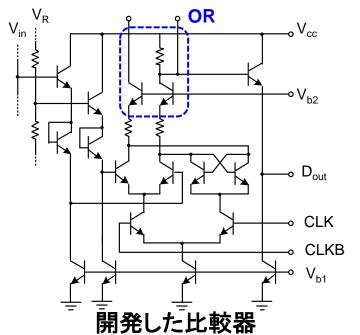

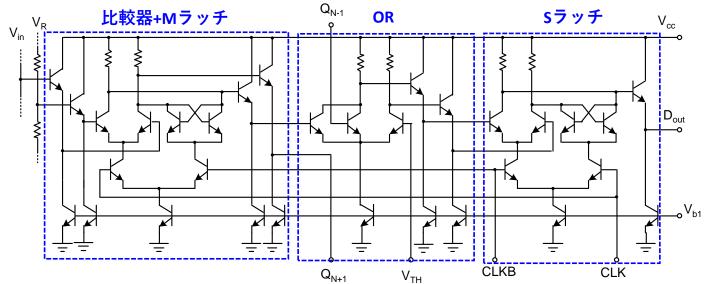

開発した比較器

### 消費電力と面積の低減方法

先行するTRW (当時存在した米, 軍用製品メーカー) の比較器はECL回路を3段使用していた

ECL回路は縦積にして、電流切替で論理を構成できるので、1段で2段分の回路を実現し、スレーブラッチを省くことで面積と消費電力を約1/3に低減した

#### 回路を簡素化することで性能向上

#### TRWの比較器

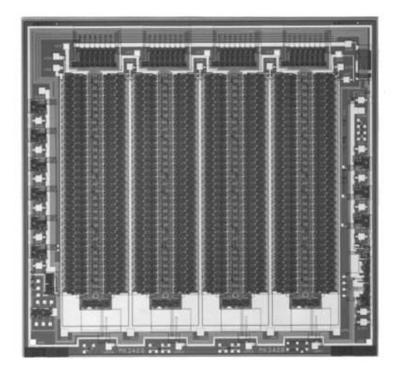

### 世界初のビデオ用 10b ADC の開発

1982年, バイポーラ技術を用いて高精度比較器を集積し, Pursuing Excellence

世界初の集積化されたビデオ用10b ADCを実現した。

Bipolar (3µm) 10b, 20MS/s, 2W \$ 800

世界初のデジタルビデオスイッチャー NTT 256QAM無線伝送 ソウル五輪のハイビジョン中継などに使用

アナログICでは世界最高の集積度 日経エレの表紙を飾る

T. Takemoto and A. Matsuzawa, JSC, pp.1133-1138, 1982.

IR100 Award受賞

### 開発したバイポーラ超高速 ADC

バイポーラと並列型ADC技術を用いて各種超高速ADCを開発。

8b, 120MHz, (1984) M. Inoue and A. Matsuzawa, ISSCC 1984 JSC. SC-19, 1984 世界最速 8b ADC

当時HDTVの広帯域カメラ信号を変換できるADCがなかった このADCの開発でHDTV用カメラが実現できた。

HDTV カメラ とデジタルオシロスコープの実現に寄与

8b, 600MHz ADC (1991)

世界最速 8b ADC A. Matsuzawa, VLSI symposia 1991

6b, 1GHz ADC (1991)

A. Matsuzawa, ISSCC 1991

量産レベルで世界最高速 デジタルオシロスコープの実現

TOKYO TECH

### デジタルオシロの実現

デジタルオシロスコープは超高速ADCの開発があってこそ実現できた

#### Yokogawa Electric 8b 1GHz (1994)

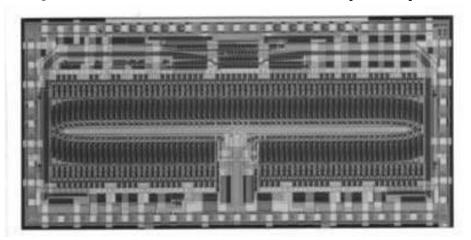

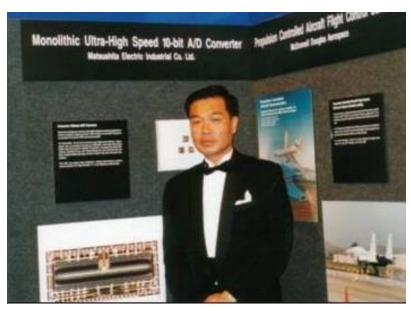

### 超高速10b 300MHz ADCの開発

複数の増幅器の出力間に補間抵抗を入れることで、オフセットばらつきへの要求を大幅に緩和、世界最高速10ビットADCを実現した。 HDTV信号の光送受信機に用いられた。

10bitで他の開発よりも4倍高速, 世界最高速

Bipolar 10b 300MHz, 4W 1.2µm Bipolar

信号線とクロック線の遅延時間を合わせるために ■ 陸上トラックや鉄道模型のようなユニークなレイアウト は美しい工業デザインに選定されニューヨークの

メトロポリタン美術館に展示された

#### 1994年 R&D100 AWARDを受賞

シカゴの受賞者ブースにて

H. Kimura and A. Matsuzawa, VLSI Symposia '92, JSC, SC-28, 1993.

### HDTVシステムの開発

次世代のデジタルTVシステム, HDTVの開発は1970年代後期からNHK技研でを中心に開始されており、当初はMUSEハイビジョン方式であった。バイポーラADCは主としてこの方式の実現に寄与した。この方式は帯域圧縮を信号の折り畳みで行うものであったが今日のHDTVはMPEGをベースとしたものに変わっている。

ハイビジョン受像機

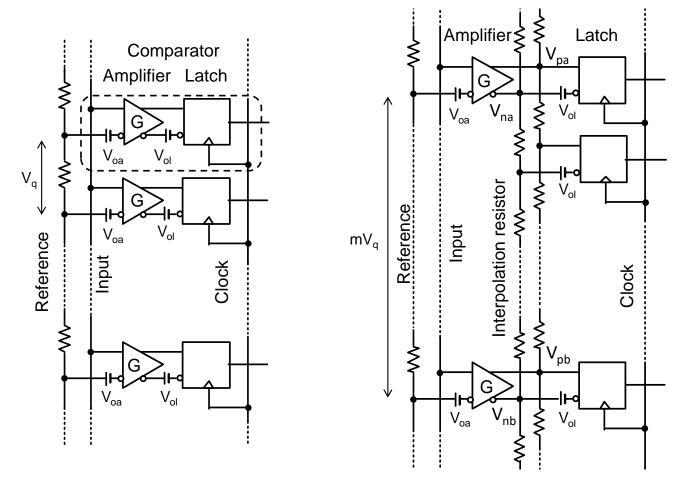

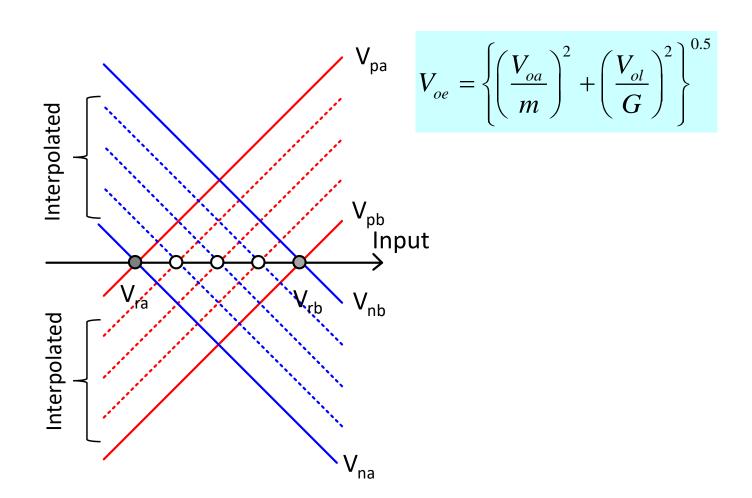

### ADCの独自技術:補間

TOKYO TECH

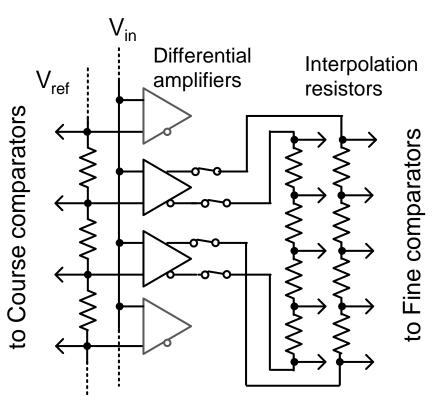

比較器はラッチと前段アンプで構成されるが、前段アンプのオフセット電圧分布がADCのDNLを劣化させる。そこで、前段アンプを1/8位に間引き、その出力間をシリーズ抵抗で結合して、タップ電圧をラッチに与える。DNLに与えるラッチのオフセットは1/G、アンプのオフセットは1/mになる。

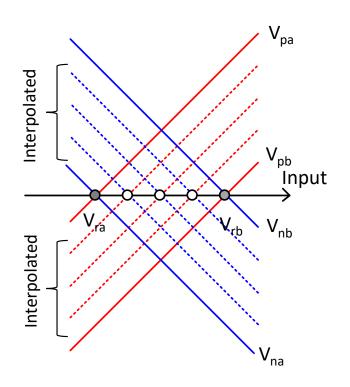

### 補間電圧

補間電圧は2つの差動出力間を均等に分圧することで、等価的に、より細かい参照電圧を作り出すことができる

### 補間の数学的表現

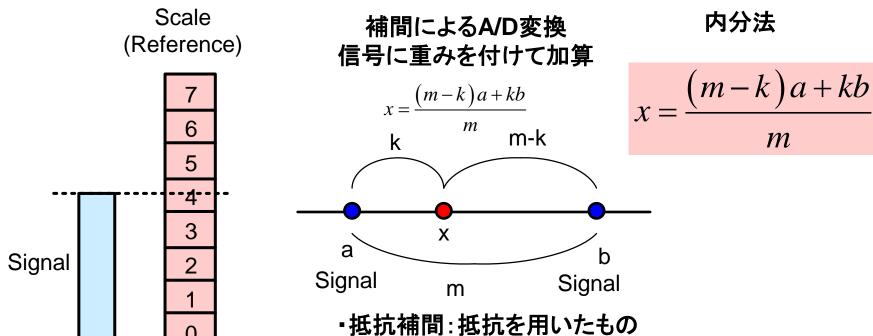

博士論文をまとめているときに、補間は数学的には内分法を表しているできたでに 気が付いた。信号に重みを掛けて加算できれば、どんな回路も補間できる。

参照電圧を持たずに、2つの信号を重みを付けて加算することで A/D変換を行うというのは、それまでなかった技術

通常のA/D変換 信号と参照電圧を比較する

・容量補間:容量を用いたもの

•ゲート補間:リニア領域の抵抗を用いたもの

・時間補間:遅延時間を用いたもの

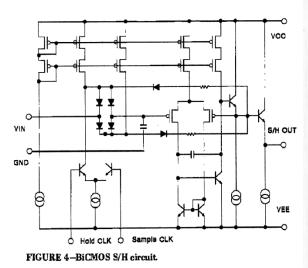

### バイCMOSの時代

1980年代の後半にはバイポーラとCMOSを集積した

バイCMOS技術が開発された。

CMOSによりサンプルホールドが使用できるようになった ので、2回程度の変換を行う直並列型ADCアーキテクチャ を採用できたことにより、消費電力を下げることができた。 しかし、2つの変換領域のつなぎが難しかった。 このため滑らかなつなぎを実現する補間技術を開発した。

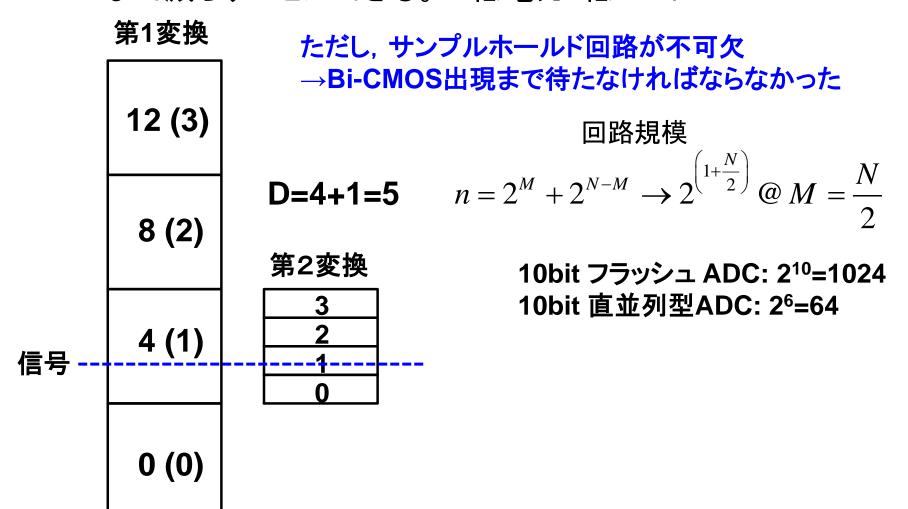

### 直並列型ADC

並列型ではコスト、量産性などに多くの課題があり、民生用は無理であった。 直並列型が回路規模の低減に有効であるが、サンプルホールド回路を必要とし、 バイポーラ回路では実現が困難であった。そこで、この課題を当時使用可能になっ ていたBi-CMOSを用いて解決した直並列型ADCを開発した。

#### 家庭用ハイビジョン受像機の開発に貢献

Bi-CMOS サンプルホールド回路 A. Matsuzawa, ISSCC 1990.

ハイビジョン受像器用ボード (世界初の家庭用HD受信機)

チップ写真

### 直並列型ADC

変換を2段階で行えれば、回路規模は分解能Nにおいて  $2^N$ 個から  $2^{(1+N/2)}$ まで減らすことができる。 $\rightarrow$  低電力・低コスト

A. Matsuzawa

**Pursuing Excellence**

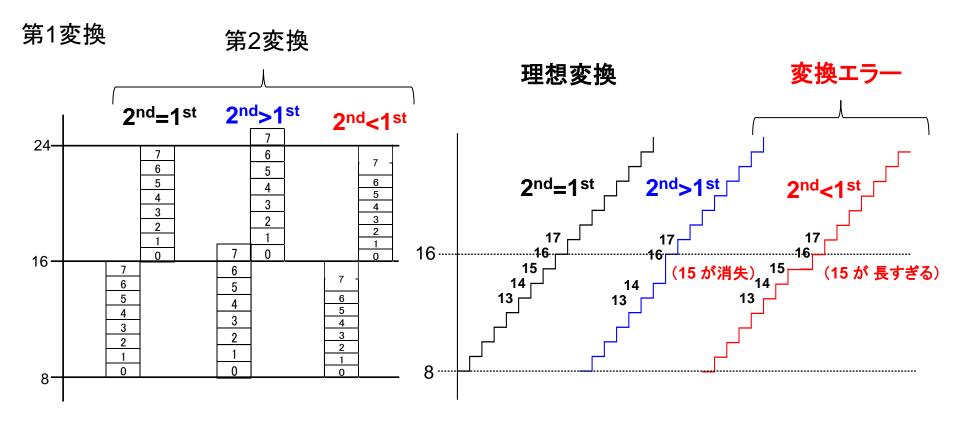

### 直並列型ADCの課題

直並列型ADCの大きな課題は、第2変換の参照電圧が第1変換の単位参照電圧と1/4LMB (0.2mV 10bit)以下で合致しなければならないこと。スイッチのフィードスルーやトランジスタミスマッチがあるので容易ではない。

A. Matsuzawa

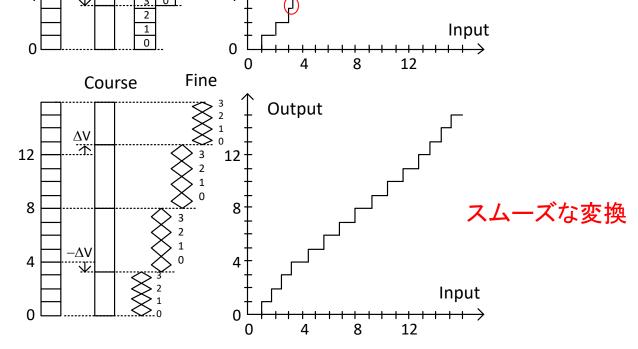

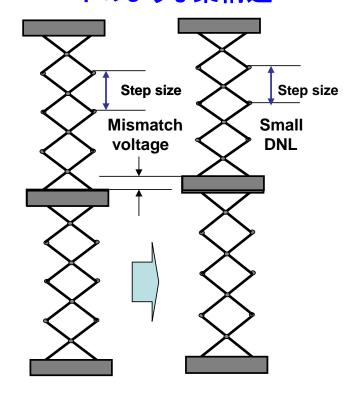

### 補間による課題解決

上位と下位のつなぎ目で精度が劣化する。この課題を補間により解決

上位変換: Mビット 下位変換: N-Mビット

#### 1994 注目発明賞受賞

### 通常変換と補間を用いた変換

Pursuing Excellence 通常、下位の参照電圧が固定なので、増幅器のオフセットなどにより つなぎ目で大きな誤差が発生する。補間では均等分圧するので誤差が分散される

Fine Course Output 3 2 1 Large error  $\Delta V$ 12 12 3 2 1 0 通常変換 8  $-\Delta V$ 参照電圧が固定

補間を用いた変換

ばねのような構造

均等分圧

# 34 FINKY D TECH Pursuing Excellence

### 超低電力CMOS ADCの開発と

ローパワーエレクトロニクスの振興

### CMOSの時代

高集積化、アナログデジタル混載など将来の発展のためにはCMOSを用いたADCの実現が不可欠であった。しかし、CMOSは精度が極めて悪く、ADCへの適用は困難であった。また消費電力も大きかった。

大きなブレークスルーは容量、スイッチ、インバータという、バイポーラでは実現困難な、CMOSの特徴を生かした回路技術により、その課題を解決したことである。その後、ADCは100% CMOSに切り替わった。

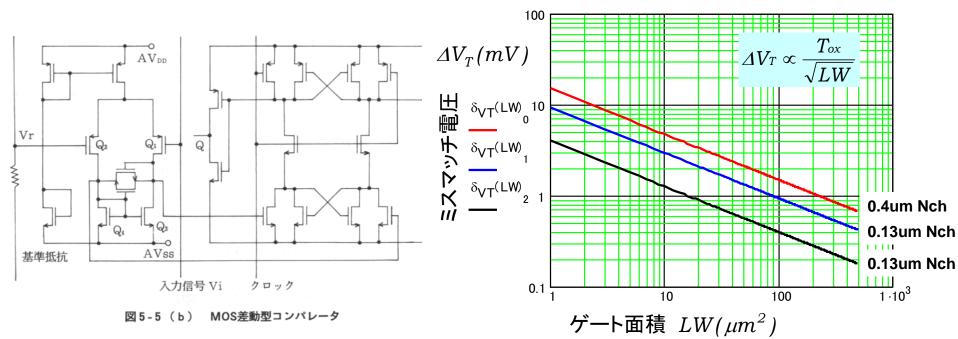

### CMOS 比較器

最初のCMOS比較器はただ単にバイポーラ回路をCMOSに焼き直したものでででであった。MOSはバイポーラに比べ約20倍以上精度が悪く(2mV vs. 0.1mV)、このため7bitくらいが限界であった。

MOSトランジスタのミスマッチを低減するためにはゲート面積を大きくする必要があり、精度を上げようとすると、コスト、消費電力が増大し、変換周波数が低下した。

MOSトランジスタのゲート面積とミスマッチ

Yukawa, et al., JSC, 1986.

東工大 松澤

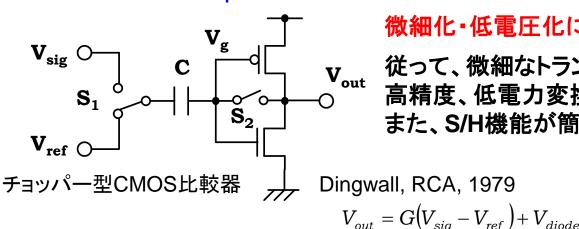

# チョッパー型CMOS比較器

CMOS ADCが高精度かつローパワーになったのはこのチョッパー型比較器の開発による。インバータ、容量、スイッチという最も単純な回路を組み合わせることで比較・増幅・オフセット電圧補償、ラッチ動作を実現した。

#### ダイオード電圧はVT変動などにより変動するが、容量Cによりキャンセル可能

微細化・低電圧化に対応し、今日でも有効な回路

従って、微細なトランジスタを用いても 高精度、低電力変換が可能になった。 また、S/H機能が簡単に実現できるようになった。

Vout

V<sub>ref</sub> C V<sub>out</sub>

$V_{g} = V_{diode}$

信号トラッキング サンプル+比較増幅

東工大 松澤

Pursuing Excellence

### CMOSによる直並列型ADCの実現

#### CMOSによる直並列型ADCを実現するには

- 1. 高精度比較器 V<sub>off</sub><1mV (通常のMOS V<sub>T</sub>ミスマッチは20mV程度)

- 2. S/H機能の実現

- 3. 低電力化

#### それでも8bitが限度であった

CMOSチョッパー比較器

S/H機能とオフセット補償を同時に実現

8bit ADC

N. Fukushima, ISSCC 1989

東工大 松澤

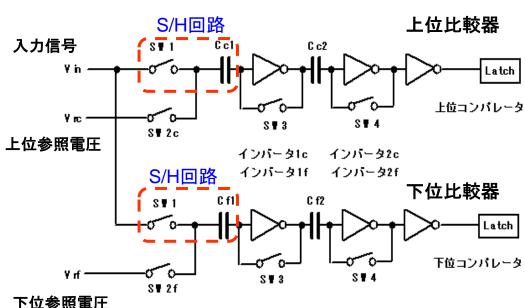

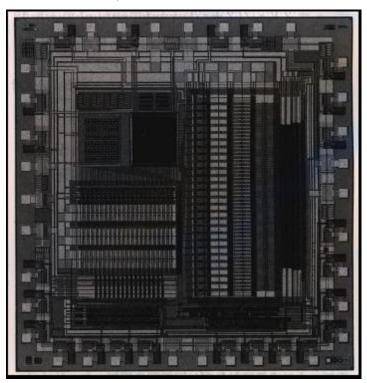

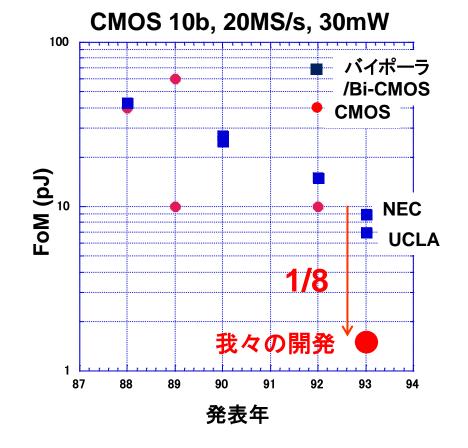

### 超低電力 CMOS 10b ADCの開発

携帯用ビデオ機器に使用できる超低電力、低コストADCの開発できる。

他のADCに比べ1/8の低消費エネルギー。これ以後、ADCのCMOS化が加速ADCのFoMはこの開発の意義を示すために考案されたと言われている

K. Kusumoto and A. Matsuzawa ISSCC '93, JSC 1993.

それまではCMOSは低エネルギではなかった

### 容量補間技術

それまでのチョッパー比較器を用いたADCの精度は8bit程度であり、Pursuing Excellence 貫通電流が流れるので、低電力化に限度があった。そこで、容量を用いて 補間を行うことで、高精度化と画期的な低電力化を同時に達成した。

#### 回路規模を削減して性能を上げ、電力を低減

K. Kusumoto and A. Matsuzawa JSC, pp. 1200-1206, 1993.

#### バネのような柔構造

入力のV<sub>off</sub>は変換時に1/4に低減

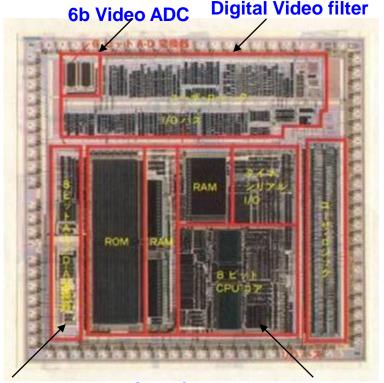

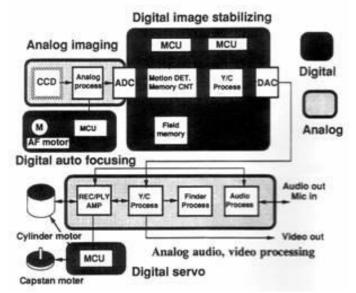

# 初期のアナログ・デジタル混載LSI

低電力CMOS ADCの開発に成功したことで、デジタルフィルターや、 Pursuing Excellence マイコンなどのデジタル回路との混載が可能となり、ポータブルAV機器の小型化低コスト化、デジタル化に大きく貢献した。

A. Matsuzawa, "Low-Voltage and Low-Power Circuit Design for mixed Analog/Digital Systems in Portable Equipment," IEEE Journal of Solid-State Circuits, Vol.29, No.4, pp.470-480, 1994.

#### 初期のアナ・デジ混載LSI

デジタル手振れ補正

System block diagram

8b low speed ADC;DAC

8b CPU

TOKYO TECH

AT PROCESSION OF THE

**Pursuing Excellence**

# ムービーカメラのディジタル化に貢献

Digital handy VCR needs CMOS ADCs and DACs

1994

CMOS 8b ADC

CMOS 8b 3ch DAC

# ローパワーエレクトロニクスの国際WS開催

1994年のVLSIシンポでのローパワー技術に関する招待講演がきっかけどなってで 1995年に世界初のローパワーエレクトロニクスの国際WSを開催した

Proceedings

of

LOW POWER ELECTRONICS WORKSHOP

June 7, 1995

Chairman:

M. Kubo, Hitachi

Co-Chairman: A. Matsuzawa, Matsushita

R.-H. Yan, AT&T Bell Labs

1995 Symposium on VLSI Circuits (June 8-10, 1995)

The Japan Society of Applied Physics The IEEE Solid-State Circuits Council

| Table of Contents                                                               |     |  |

|---------------------------------------------------------------------------------|-----|--|

| New Wireless Phone System: PHS                                                  | 1   |  |

| Low Power DSP Design Methodologies                                              | 11  |  |

| Architectures and RF Circuits for Miniature Wireless Transceivers Asad A. ABIDI | 29  |  |

| VCR Combined with a Video CameraJun HIRAI                                       | 65  |  |

| To Realize Long Battery Life of Portable PCShimpei KUNII                        | 71  |  |

| PDA: Personal Information Tool (PIT) Satoshi TERAMURA                           | 79  |  |

| RISC Processor for Mobile Computing                                             | 87  |  |

| Memory for Personal Computing                                                   | 97  |  |

| Technology Advances in Liquid-Crystal Displays                                  | 107 |  |

| Rechargeable Batteries for Portable AppliancesAkira OHTA                        | 117 |  |

### 低電力LSIの技術白書

アナログ回路だけでなく、デジタルLSIのアーキテクチャまで踏み込んで ローパワー技術を検討していた。日経BP社:日経マイクロデバイス編 1994年

設計/ロジック/アーキテクチャ

[低電力LSIの技術白書 1ミリ・ワットへの挑戦]

1mW台に挑戦するアーキテクチャ

高速化から視点を切り替える

低電力アーキテクチャとは何か、今後のLSI市場でどのような役割を果たすのか、 を解説する。低電力アーキテクチャとは、所望の機能を達成しながら低電力化す るアーキテクチャである。高スループット化技術と、無駄なスイッチングを減ら す技術が2本柱になる。こうした低電力アーキテクチャは、専用LSIに適用する 場合が多くなる。ネットワークの整備により、低電力で処理性能の高い専用LSI が普及しやすくなった。汎用LSIと補完しながら、マルチメディア時代を創る。

松下雷器産業 半導体研究センター 松澤 昭

設計/ロジック/アーキテクチャ

Part. 2

**画像向け**などアーキテクチャを専用化 チップ面積を抑えつつ雷力削減

専用回路と汎用回路の双方を搭載する専用プロセサは、チップ面積の増加 を極力抑えながら低電力化できる。このアーキテクチャ設計の考え方と手 法を分類し、系統的に解説する。さらに、ディジタル携帯電話向け音声処 理DSPや、MPEG2などの画像処理DSPに適用したアーキテクチャをケ ース・スタディとして挙げる。低電力化の際の狙いどころの絞り方や、チ ップ面積をほとんど増やさずにスループットを高める手法などを示す。

松下雷哭産業 半導体研究センター 松澤 昭 上田 勝彦 青野 邦年

スループット(処理性能)を劣化させないアーキテクチャ・レベルの低電力手法

図3●低電力アーキテクチャの手法の全体像

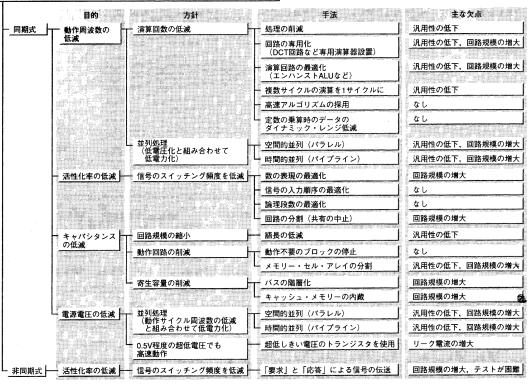

司期式と非同期式がある。動作時の消費電力は主に、動作周波数と活性化率、キャパシタンス、電源電圧で決まる。これらを低減する手法を分類した。

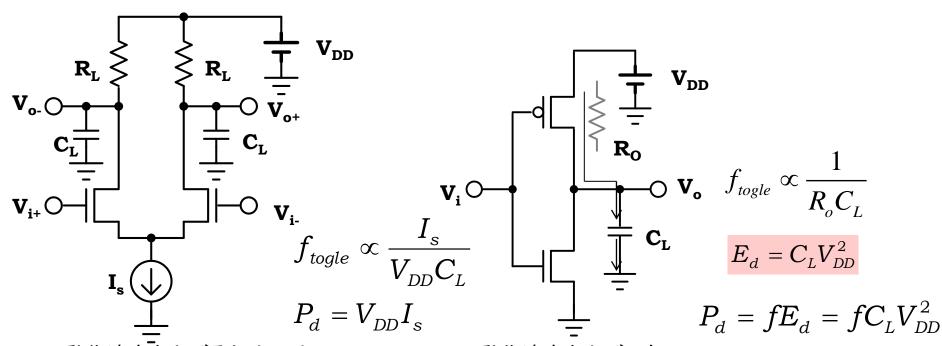

### ロジック回路の進歩

TDKYD TECH Pursuing Excellence

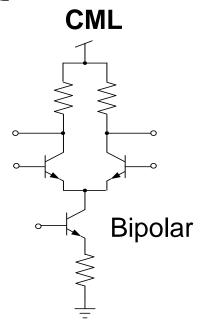

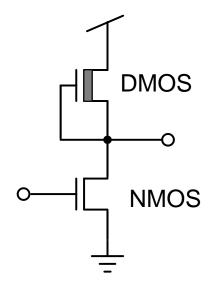

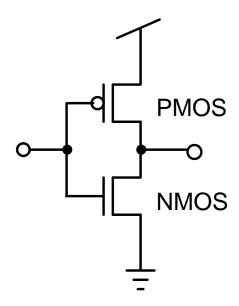

ロジック回路は電流の切り替えを行うCML, EDMOSから電流ではなく電荷の切り替えを行うCMOSに進化し、低電力動作とテクノロジスケーリングが可能になった

定常電流が流れる

メインフレーム 1960-1990

#### **E/D NMOS**

定常電流が流れる

PC 1970-1985

A. Matsuzawa

#### **CMOS**

#### 定常電流が流れない

Watch, Calculator, PC, Everything 1970-Present

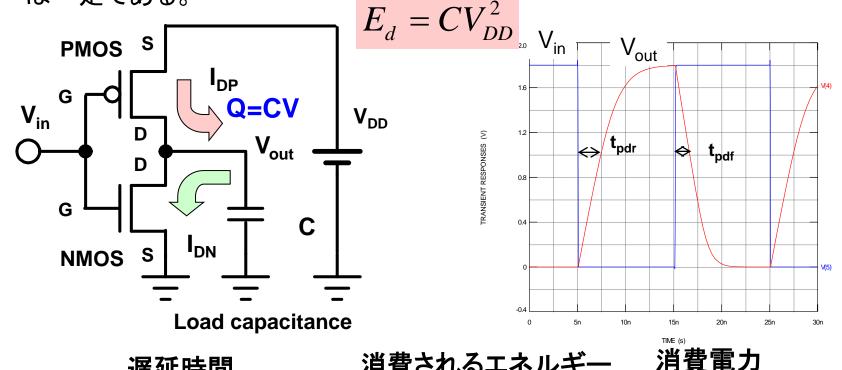

### CMOSロジックの特徴

CMOSロジックはPMOSが負荷容量に電荷を与え"H"状態にし、NMOSが電荷を 放電することで"L"状態にする。定常電流が流れず、消費エネルギーは電源から 注入された電荷で決まる。高速動作では充放電電流は増えるが,消費エネルギ 一は一定である。

#### 遅延時間

$$t_{pdr} = \frac{CV_{DD}}{2I_{DP}}, t_{pdf} = \frac{CV_{DD}}{2I_{DN}}$$

#### 消費されるエネルギー

$$E_d = CV_{DD}^2$$

$$P_d = fCV_{DD}^2$$

A. Matsuzawa

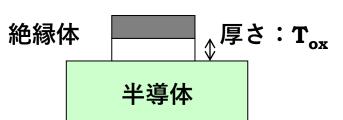

### スケーリング則

微細に作ると、面積当たりのトランジスタ数が増やせるのでトランジスタあたりのコストは安くなる。しかも遅延時間が短くなり、演算速度が上がり、消費電力が下がる

#### トランジスタを一定比率で縮小する

スケーリング

工学院 松澤 昭

### スケーリング則:集積回路技術の基本原理

Pursuing Excellence

スケーリングによりLSIの集積度と性能が向上し、消費電力とコストが下がる

寸法縮小率: 0.7

面積縮小率: 0.5

スケーリング

| 電界が一 | -定になる | 。<br>ようにする |

|------|-------|------------|

|------|-------|------------|

|                         | スケーリングファクター        |

|-------------------------|--------------------|

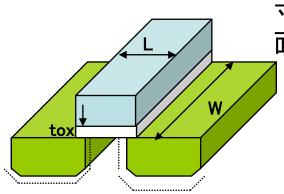

| トランジスタのパラメータ: L, W, Tox | 1/S                |

| 不純物濃度                   | S                  |

| 電圧                      | 1/\$               |

| 電界                      | 1                  |

| 流れる電流                   | 1/\$               |

| 遅延時間                    | 1/\$               |

| 消費電力                    | $1/S^2 \sim 1/S^3$ |

| トランジスタの大きさ              | $1/S^2$            |

| トランジスタのコスト(参考)          | 1/S                |

$$S \approx \sqrt{2}$$

スケーリングファクターSは 1世代につき 1.4に設定する

スケーリングにより殆ど すべての性能を向上できる

工学院 松澤 昭

### CMOS論理回路の遅延時間

次段のインバータは容量に見える<br/>ゲート容量 ゲート (金属)

$$T_{pd} pprox rac{CV_{DD}}{2I_{D}} \quad C = C_{ox}LW = arepsilon rac{LW}{T_{ox}}$$

$I_{D} pprox KC_{ox}W(V_{GS} - V'_{T}) \qquad C_{ox} = rac{arepsilon}{T_{ox}}$   $= KC_{ox}W(V_{DD} - V'_{T}) \quad \text{K: 比例定数}$

$$T_{pd} pprox rac{CV_{DD}}{2I_{D}} = arepsilon rac{LW}{T_{ox}} rac{T_{ox}V_{DD}}{arepsilon KW(V_{DD} - V'_{T})}$$

$$=\frac{L}{\mathit{K}\!\!\left(1\!-\!\frac{{V'}_{T}}{V_{DD}}\right)}$$

$$T_{pd} pprox rac{L}{\mathit{K}\!\!\left(1\!-\!rac{{V'}_{T}}{V_{DD}}

ight)}$$

工学院 松澤 昭

# スケーリング則の検証

TOKYO TECH Pursuing Excellence

#### MOSトランジスタをスケーリングすれば速度が上がり消費電力が下がる

$$I_{dsat} \approx \frac{v_s C_{ox}}{2} W (V_{dd} - V_T)$$

$$I_{dsat} \rightarrow s \times \frac{1}{s} \times \frac{1}{s}$$

$$C_L \propto C_{ox} \cdot L \cdot W \rightarrow S \times \frac{1}{S} \times \frac{1}{S} = \frac{1}{S}$$

$$T_{pd} \approx \frac{C_L V_{dd}}{I_{dsat}} \rightarrow \frac{\frac{1}{s} \cdot \frac{1}{s}}{\frac{1}{s}} = \frac{1}{s}$$

$$p_d \propto fC_L V_{dd}^2 \rightarrow f \frac{1}{s} \cdot \frac{1}{s^2} = f \frac{1}{s^3}$$

前提条件として しきい値電圧はスケールできる 負荷容量はゲート容量のみで決まる

(しかし、実際はこうはうまくはいかない)

$$C_{ox} o s$$

$W o rac{1}{s}, L o rac{1}{s}$

$V_{gs} = V_{dd} o rac{1}{s}$

$$V_T \to \frac{1}{s}$$

**Pursuing Excellence**

# アダプティブ電源内蔵MTDSPの開発

95年よりNTTとMTCMOSなどのローパワー技術の共同開発を行った。

電源電圧の制御は時代を先取りする技術。

要求動作周波数に対して最小の消費電力になるよう内部電圧を制御してローパワー化を図ったDSP

#### 腕時計型携帯電話を開発

S. Sakiyama et al., VLSI CS '97, 12mW @20MHz 0.35um MTCMOS

#### 長野五輪(1998年)で係員用PHSに実際に使用された。

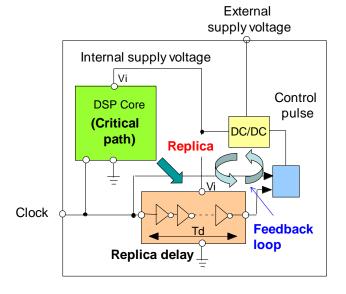

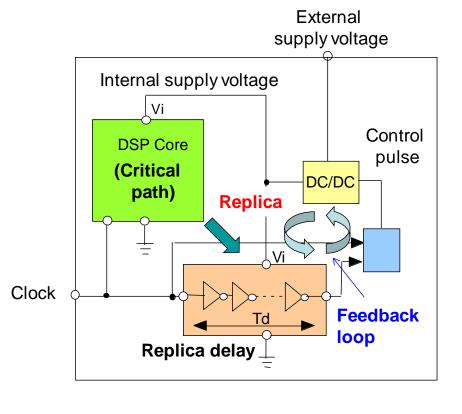

### アダプティブ電源を内蔵したDSPの開発

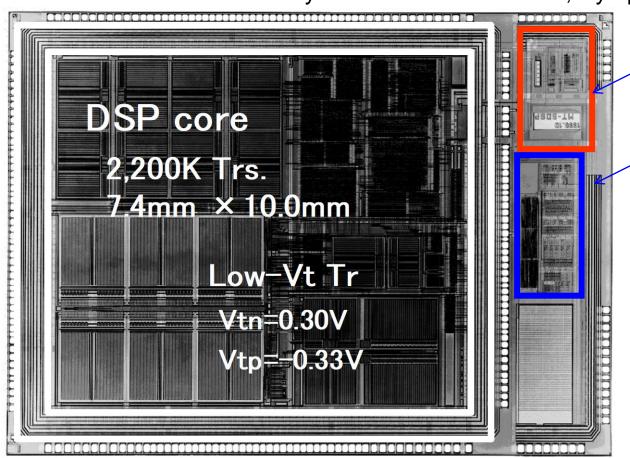

DSPに動作状態を検知し、動作電圧を制御するアダプティブ<sup>Pursuing Excellence</sup> DC/DC電源を集積した携帯電話用DSPを開発した

S. Sakiyama and A. Matsuzawa, Symp. on VLSI Circuits 1997

Adaptive supply voltage control circuits

On chip DC/DC

0.35umCMOS 2.2M Tr 20MIPS 12mW (1.2V, internal)

Leakage current 500uA: active 1uA: standby

A. Matsuzawa

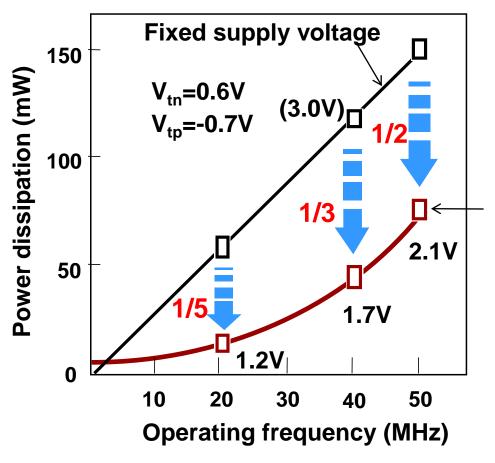

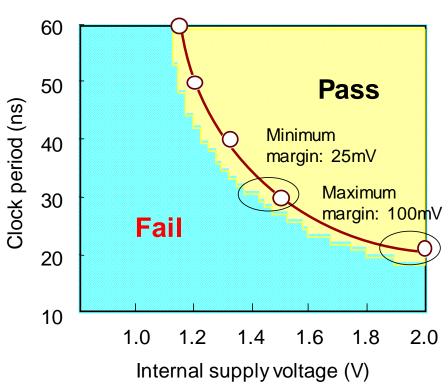

### アダプティブ電源

DSPの処理速度が遅くても良い場合は、電源電圧を下げてロジックの速度を 遅くしても良い。このことで消費エネルギーを下げることができる。

50MHz動作→2.1V, 20MHz動作→1.2V 消費エネルギーは約1/3

$$E_d = CV_{DD}^2$$

$$P_d = fCV_{DD}^2$$

Adaptive supply voltage +Low VT transistors

$$(1.0V--2.2V)$$

$$V_{tn} = 0.30V$$

$V_{tp} = -0.33V$

A. Matsuzawa

Pursuing Excellence

### 最小動作電圧の検知

DSPのクリティカルパスを模擬したレプリカ遅延回路を設け基準の遅延時間になるようにDC/DC変換器の出力電圧を制御する

A. Matsuzawa

2000年から4年間のNTTを中心とする複数の企業・大学によるNEDOプロジェグド。 低電圧・低消費電力に優れた、FDSOIを用いてマイコン・メモリ・アナログRF回路を 開発し、体温などの自然エネルギーで動作する無線PDA端末を開発した。 松下は低電圧アナログRF回路開発を担当。

プロジェクト概要はSpringerから出版された

#### Getting energy from temperature difference

Using heat of a hand

Using cold water

Bi-Te based thermoelectric converter

Battery-less wireless signal transmission using temperature difference

Douseki, et al., ISSCC2003,

•1.7mW/ 0.7Vを発電

FIDKYD TECH-Pursuing Excellence

28.7

# パイプライン型 ADC

ADCの高精度化・高速化に寄与したのはパイプライン型ADCである。性能はOPアンプで決まるため、CMOS OPアンプ技術が発達した。

ただしOPアンプは微細化・低電圧化により性能が出しにくくなっているので最近はSAR ADCが主流になっている。

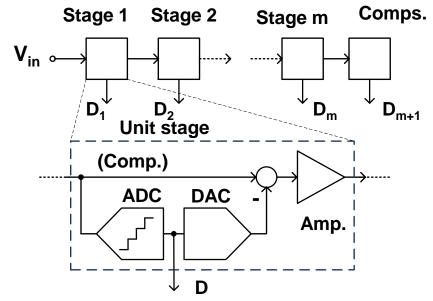

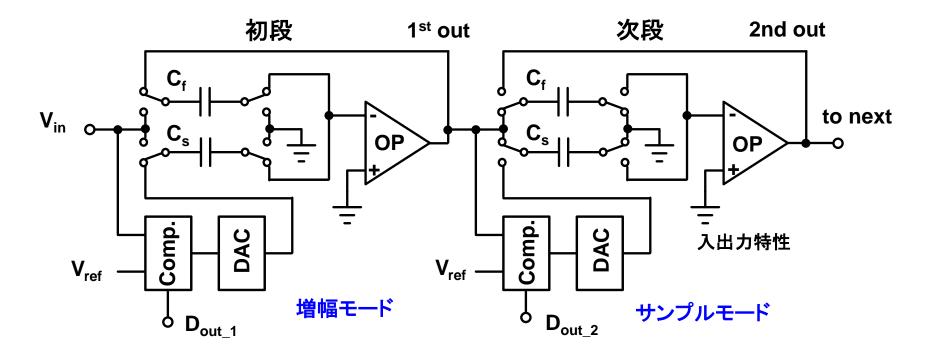

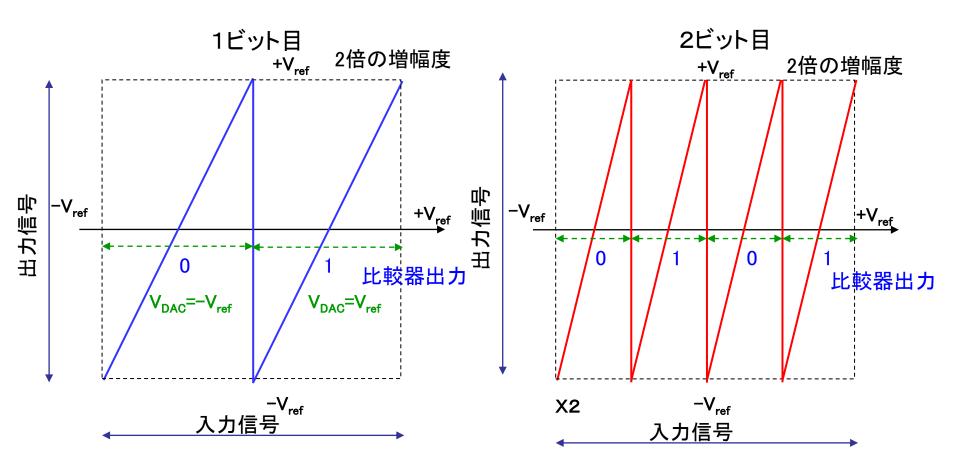

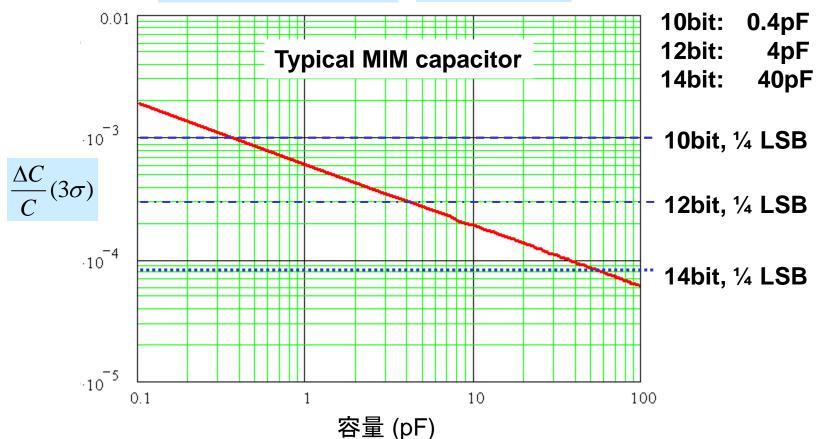

### パイプライン型ADC

#### パイプライン型ADCは以下の動作をパイプライン的に繰り返す

- 1. 比較器で各段の入力信号と参照電圧と比較し、変換値(デジタル)を発生する

- 2. 比較器の出力に応じてDACを制御し、OPアンプによるSCF回路により入力信号とDAC信号の差分電圧を増幅して(2倍が多い)出力する

- 3. 次段は前段の出力信号をサンプリングする

### パイプラインADCの入出力関係(基本)

信号を折れ返して転送することにより1ビットずつ変換を行う 2倍の増幅度を保つと、信号振幅が一定で信号転送が可能 1ビットの単位回路を従属接続することで分解能を容易に上げられる

rokyo tech-

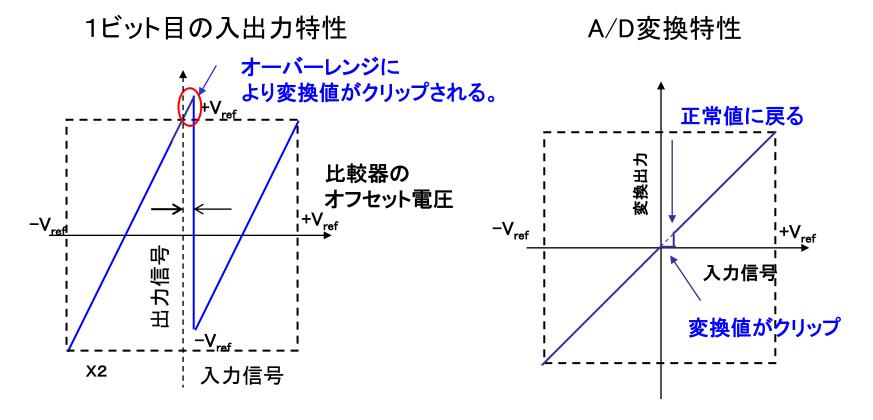

当初パイプライン型ADCは実用には至らなかった。比較器にオフセットがあると、出力信号が変換範囲(点線で囲んだ領域)を逸脱し、変換特性では変換値がクリップされるため。オフセット電圧は10bitで0.5mV, 14bitで0.06mV程度が要求される。

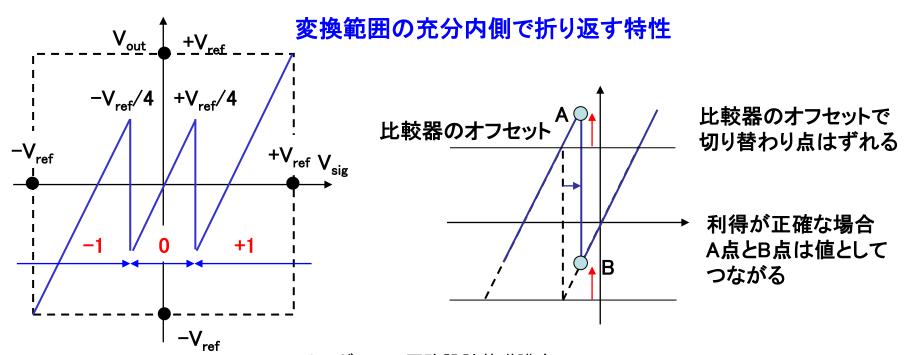

### 1.5bit冗長構成

TOKYO TECH-Pursuing Excellence

パイプラインADCが実用化されたのは1.5bit冗長構成の発明に拠るところが大きい折り返しの入力電圧をゼロではなく+/-V<sub>ref</sub>/4にすることで、出力電圧は変換範囲の十分内側で折り返すので、変換範囲を逸脱することがなくなった。 比較器のオフセット電圧は全く問題なくなったため、パイプライン型ADCは急速に普及した。

#### 1.5ビット冗長構成の変換特性

### パイプライン型ADCの精度と速度

パイプライン型ADCの性能はOPアンプ周りの性能で決定される。

#### 1. 精度

$$\frac{\Delta C}{C} < \frac{1}{2^N}$$

0.006%: 14b

容量の性質

有度

1) 容量ミスマッチ

$$\frac{\Delta C}{C} < \frac{1}{2^N}$$

$\frac{\Delta C}{C} = \frac{k}{\sqrt{C}}$   $C > k^2 2^{2N}$  分解能が1ビット上がると

4倍の容量が必要

2) 熱雜音

$$C > 18kT \left( \frac{2^N}{V_{ref}} \right)^2$$

分解能が1ビット上がると 4倍の容量が必要

3) OPアンプ利得

$$G > 3 \times 2^N$$

$G > 3 \times 2^N$  G(dB) > 6N + 10

分解能が1ビット上がると 2倍の利得が必要

70dB: 10b

94dB: 14b

2. 速度

$$GBW_{open} > Nf_c$$

分解能の依存性は低く 変換周波数に比例した GBWが必要

> 1GHz: 10b, 100MS/s 10GHz: 10b: 1GS/s

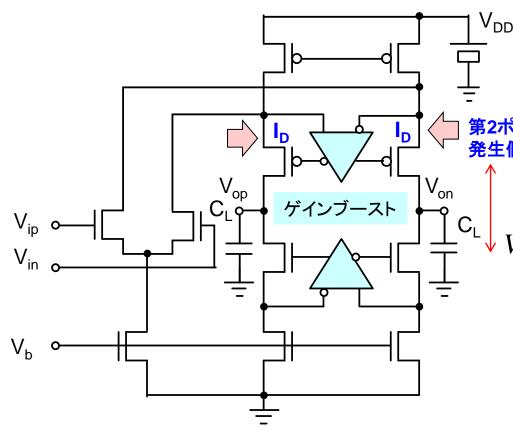

### OPアンプの本質的課題

OPアンプの高速化にはチャネル長短縮が必要だが、耐圧の低下を招き Pursuing Excellence 微細化に限界がある。また本質的に大きな定常電流が流れる。

0.35µm~90nmくらいまでは妥当だが、それ以下では適用が困難になった。

利得はゲインブーストで上げることができる

#### 1. 電源電圧

$$V_{o_{-}pp}$$

$< 2(V_{DD} - 4V_{eff})$  出力振幅 $V_{opp}$ の下限を1.0V  $V_{eff}$ を0.2Vとすると  $V_{DD}$ >1.3(V)

#### 2. 必要電流

$$GBW \approx \frac{g_m}{2\pi C_L} = \frac{2I_D}{2\pi V_{eff} \cdot C_L} > Nf_c$$

$$I_D > \pi V_{eff} C_L Nf_c$$

C\_は分解能で決まるのでスケーリング不可動作電流はスケーリングできない

**3. 変換周波数限界** f<sub>p2</sub>:第2ポール L:チャネル長

$$GBW < \frac{f_{p2}}{2} \propto \frac{1}{2I} V_{DD} \propto L$$

GBWを上げるにはチャネル長Lの短縮が必要 しかしトランジスタ耐圧が下がる

TOKYO TECH Pursuing Excellence

### SAR ADCの革新

33.6

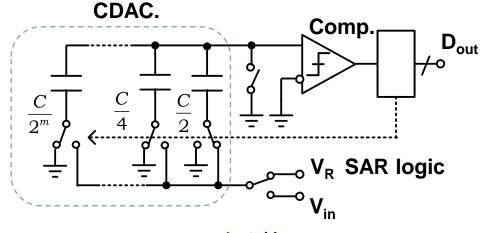

SAR (逐次比較) ADCは1970年代から使用されてきたアーキテクチャであるが、近年急速に性能を上げるとともにエネルギー消費を下げており、面積も小さいため現在の主流ADCとなっている。

容量のみで構成され、定常電流を流さないダイナミック動作 により究極の低エネルギー動作が可能である。

CMOS微細化の恩恵を直接受け、低電圧動作も可能なため 主流の位置は当面揺らぎそうもない。

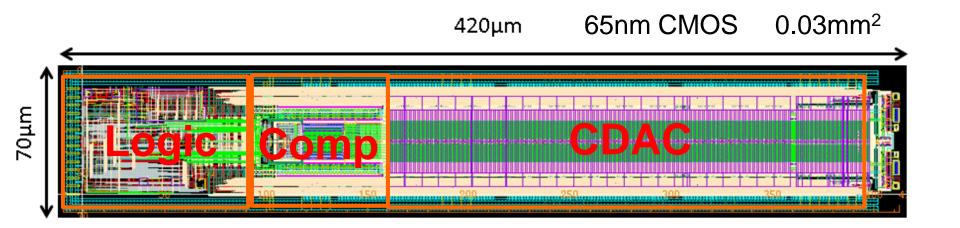

#### SAR ADC

#### SAR ADCは最も単純かつ低消費電力で小面積なADCである

S. Lee, A. Matsuzawa, et al., SSDM 2013

標本化

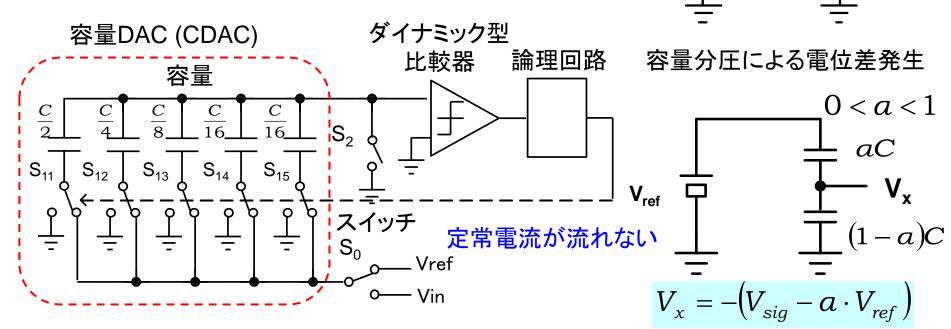

# 逐次比較型 (SAR) ADC

#### SAR ADC はADCとして最もシンプルな構成である

- 1. 標本化動作:スイッチと容量

- 2. 参照電圧発生:容量分圧による入力との電位差発生

- 3. 比較:ダイナミック比較器による比較

変換速度と消費エネルギーは論理回路で決まるので テクノロジースケーリングが有効である

ただし、ノイズはCDACと比較器の容量で決まる

#### CMOS論理回路のようなADCの構成が鍵

- ・ 高速動作でも低速動作でも回路は同じ

- 消費電力は、与えられた変換クロック周波数に自動的に比例する

- クロックが止まったら電源電流は流れない

CML 論理回路 通常の増幅器

CMOS 論理回路.

動作速度を上げるためには 消費電流を増やさなければならない 動作速度を上げても 消費エネルギーは増えない

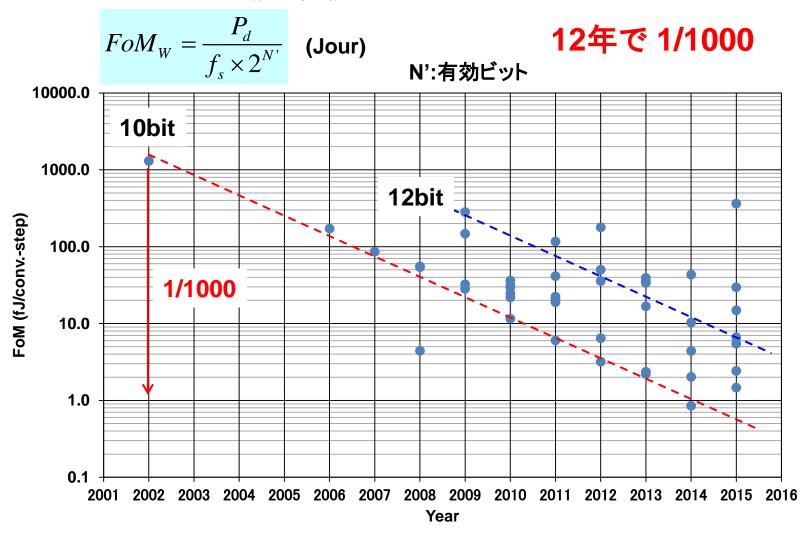

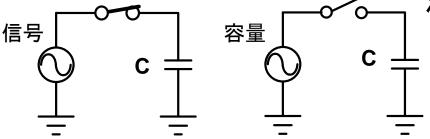

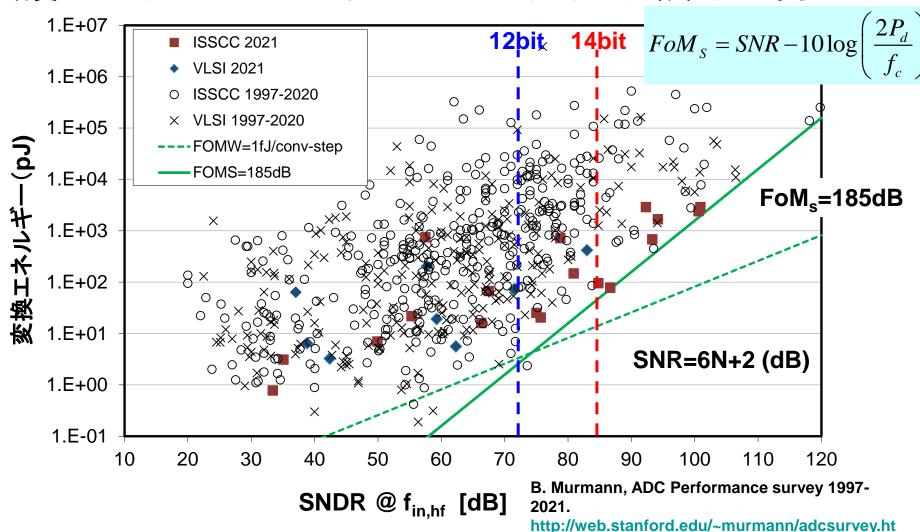

### ADCの変換エネルギー低減の進歩

ADCの消費電力が大きく、機器開発のネックであったが Pursuing Excellence ここ15年は大幅に変換エネルギーが低下した

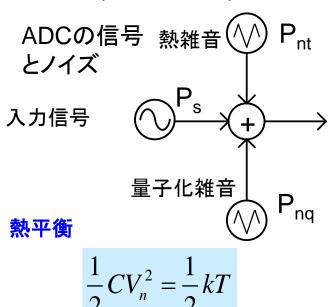

### SNRと消費エネルギーの物理

高分解化(=低雑音化)には大きな容量が必要で必然的に消費エネルギ→が増大する

量子化電圧

$$V_q = \frac{V_{FS}}{2^N}$$

$V_{FS}$ : フルスケール電圧 N: 分解能

$$P_{nq} = \frac{1}{3} \left( \frac{V_q}{2} \right)^2 = \frac{V_{FS}^2}{12 \cdot 2^{2N}}$$

熱雑音電力

必要容量

$P_{nt} = m \frac{kT}{C}$  m: ノイズ源の数

$$C = 12mkT \frac{2^{2N}}{V_{ES}^2} \qquad P_{nq} = P_{nt}$$

#### 静電エネルギー=熱エネルギー

Hold **Track** S & H circuit

消費されるエネルギー

**C**

$$=$$

$= 2C \left(\frac{V_{FS}}{2}\right)^2 = 6mkT \cdot 2^{2N} \approx 5 \times 10^{-20} \times 2^{2N} (J)$

$$E_{w} = 10^{\left(\frac{SNR(dB)-190}{10}\right)}(J)$$

2020.12.11

# 分解能 (SNR)と変換エネルギー

原理的にADCは分解能が1ビット上がると消費エネルギーは4倍に増加するExcellence 消費エネルギーが下がっているのはSARアーキテクチャと微細化の寄与

ml.

Pursuing Excellence

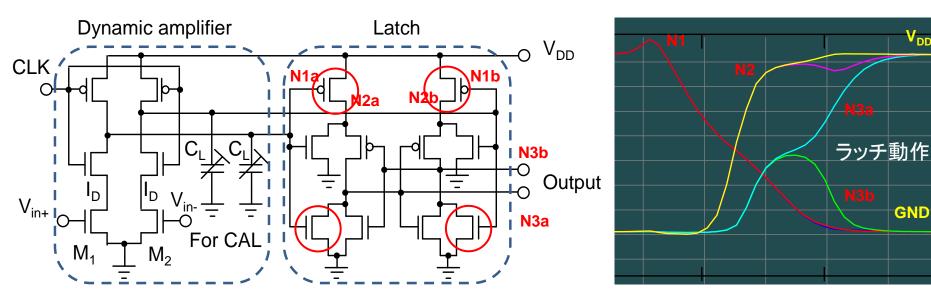

# ダイナミック型比較器の開発

ダイナミック型比較器はCMOSロジックと同様<mark>貫通電流がゼロ</mark>で動作する。 ただしノイズが大きく10bit以上の高分解能化が困難であったが、低ノイズ回路の 開発により12bitの高分解能化が可能となった。

#### ( ) 低ノイズ化のために挿入したトランジスタ

M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, "A Low-Noise Self-Calibrating Dynamic Comparator for High-Speed ADCs." A-SSCC. Nov. 2008.

Yusuke Asada, Kei Yoshihara, Tatsuya Urano, Masaya Miyahara, and Akira Matsuzawa, "A 6bit, 7mW, 250fJ, 700MS/s Subranging ADC," A-SSCC, 5-3, pp. 141-144, Taiwan, Taipei, Nov. 2009.

# ダイナミック型比較器のノイズ

ラッチの前にCMOS増幅器を設けた構成にすることで、ノイズを低減させた。 またノイズレベルは負荷容量でほぼ決定される。

A. Matsuzawa, ASICON 2009, pp. 218-221, Oct. 2009.

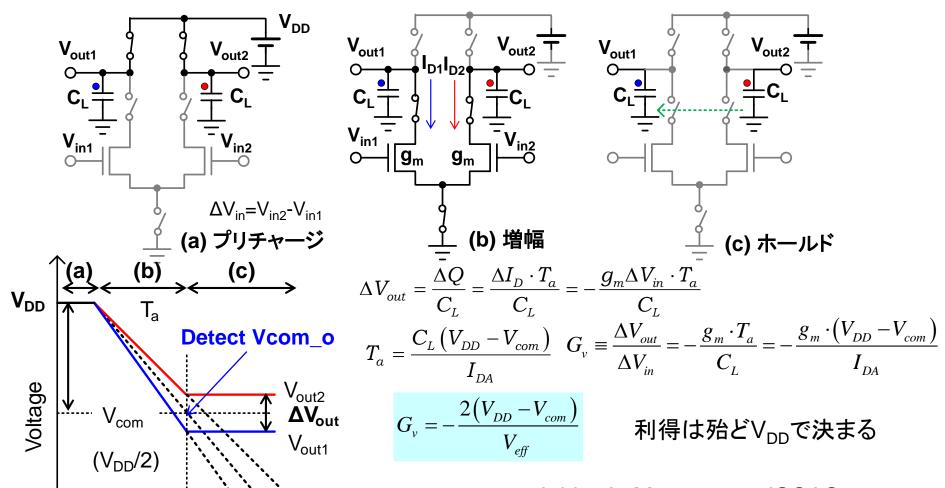

# ダイナミックアンプの開発

ダイナミックアンプは定常電流が流れず超低電力であり6倍程度の利得でいた。 実現できる。消費エネルギーは負荷容量の充放電のみ。

J. Lin, A. Matsuzawa, ISCAS 2011.

A. Matsuzawa

Time

**74**

#### 容量ミスマッチ

#### 容量ミスマッチを小さくするには大きな容量が必要

$$\frac{\Delta C}{C} (3\sigma) = \frac{6 \times 10^{-4}}{\sqrt{C (pF)}} \left( \frac{\Delta C}{C} \right)^2 \propto \frac{1}{C}$$

Pursuing Excellence

#### 直線性の向上

容量誤差や寄生容量による直線性劣化に対し、微小容量とデジタル補正回路を用いて直線性を向上させた

Capacitance mismatch CAL Floating capacitance CAL **Split capacitor** 26C Comp. 000000000 12bit SAR **Main CDAC** Capacitance mismatch CAL Floating capacitor CAL 12bit **Before** 54321012345 2 INL [LSB] After **Before** INL[LSB] After : 2 0 2 4 [8S] NI 2048 2176 2304 2432 2560 **OUTPUT CODE** 0 1024 4096 2048 3072

2020.12.11 A. Matsuzawa

**OUTPUT CODE**

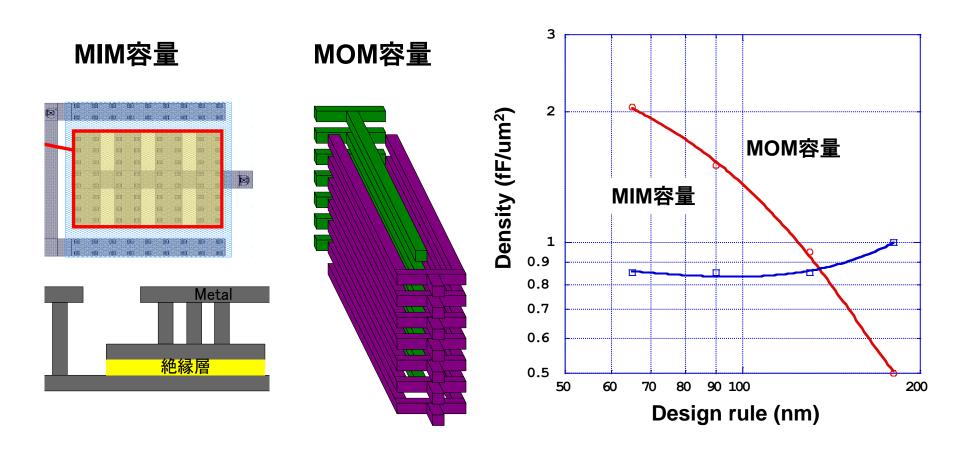

## MIM容量の限界とMOM容量

絶縁層を上下の金属で挟んだMIM容量は高精度な大容量を必要とする / Pursuing Excellence パイプライン型ADCでは最適であったが、fF以下の微小容量を必要とする SAR ADCでは使用できなくなり、配線の側面容量を用いるMOM容量が最適になった 微小容量が形成でき、微細化と配線の多層化により高密度になるため。

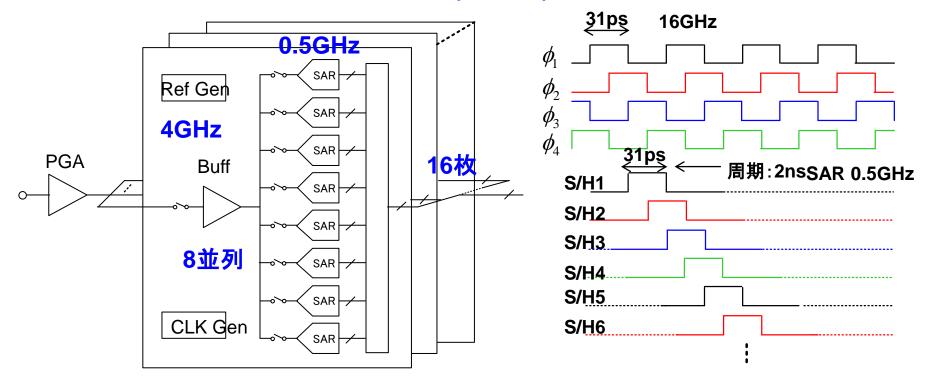

## SAR インターリーブADC

#### 光通信用9bit 64GS/s ADC

SAR ADCは面積が小さく、低電力なので超並列動作に向いている時間をずらしたインターリーブ動作により等価的に超高速動作を実現しているバックグラウンドCALなどが重要技術

128タイムインターリーブSAR ADC (64GS/s)

J. Cao, et al., ISSCC 2017, S29.2

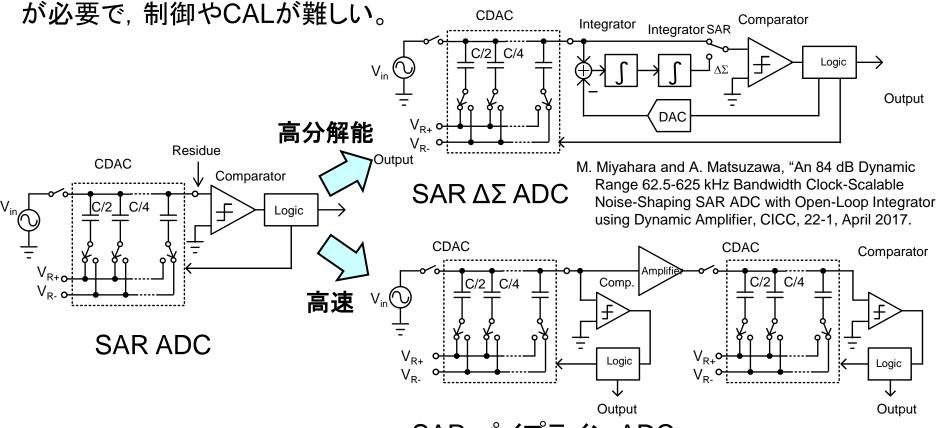

#### ハイブリッドADC

SAR ADCはCDAC内に残差信号が残っているので、この信号を他の変換形式。"on ADCに渡すことができる。したがってハイブリッド化し易い。

12ビット以上の分解能はΔΣADCでなければ実現しにくいためSAR-ΔΣADCは 重要な方向性である。パイプライン化により高速化が可能だが、ダイナミックアンプ

SAR パイプライン ADC

A. Matsuzawa

## ビデオ用ADC発展のまとめ

バイポーラからCMOSへの変遷やCMOSの微細化に伴ってADC変換技術が発展し、各種電子機器を実現した。

バイポーラ

高精度,S/H機能不可,

フラッシュのみ(10bit まで)

バイCMOS

S/H機能, 直並列型

フラッシュより低電力・低コスト

ビデオスイッチャ 初期のHDTVシステム デジタルオシロ

家庭用HDTV受像機

**CMOS**

直並列

チョッパーインバータ技術により

高精度化, 低電力化

デジタルハンディーカム

パイプライン

CMOS OPアンプ技術, 高速

14ビット程度まで高分解能化可能

微細化, 低電圧化, 低電力化に限界

CCDカメラ デジタルTV 無線通信システム

SAR

超低電力, 小面積, 微細化可能

超並列化で超高速化可能

各種センサシステム 無線通信システム 光通信システム

#### 低電力超高速ADCの開発と

アナログ・デジタル混載システムLSIの開発

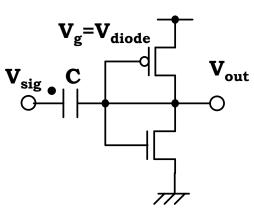

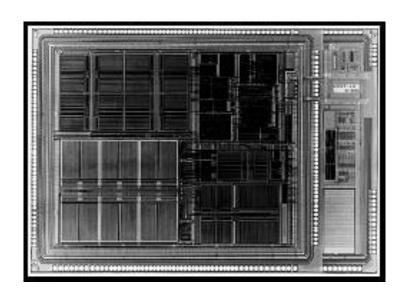

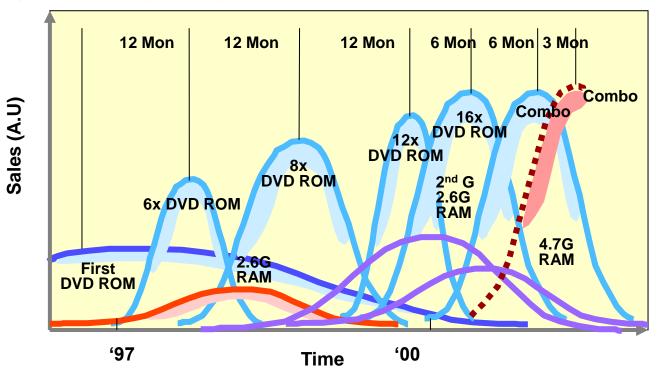

## SoC:システム集積の時代

44.1

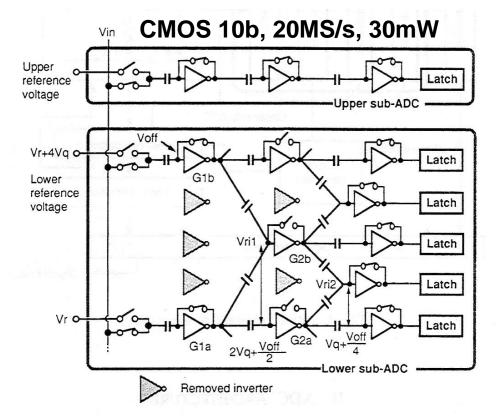

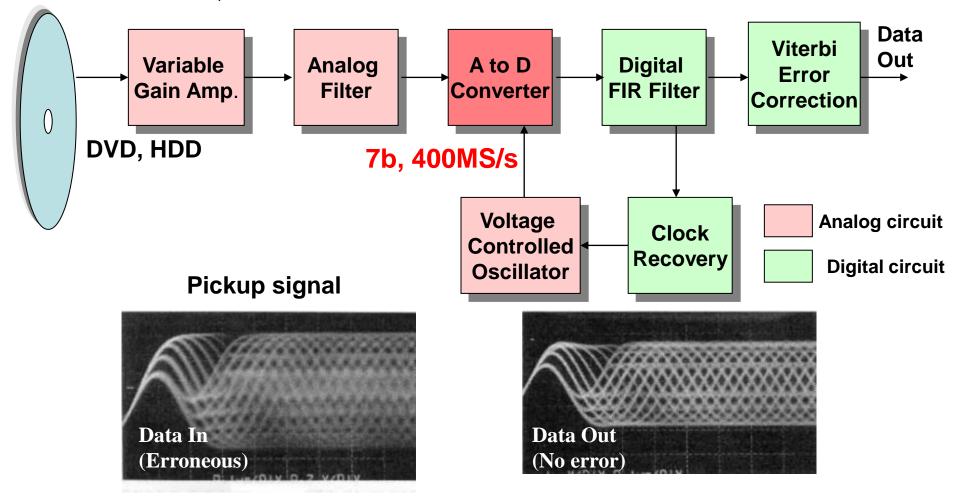

CMOS集積回路の微細化による高集積化,高性能化,低電力化の進展はDVDなどの大規模システムのワンチップ化に進んだ。ここでも一つの難関はADCであった。7bit 400MS/sという計測器なみの性能を数10mWの消費電力で実現する必要があった。これをゲート補間という技術で乗り越えた。

#### DVD再生用デジタル信号処理技術

DVDレコーダーは多値信号のためSNRが低く、誤り率が高い。 Pursuing Excellence そこで波形等価やエラー訂正などのデジタル信号処理が必要となった。 しかしそれは7b,400MHzという計測器なみのADCを必要とすることであった。

10mW/Gsps

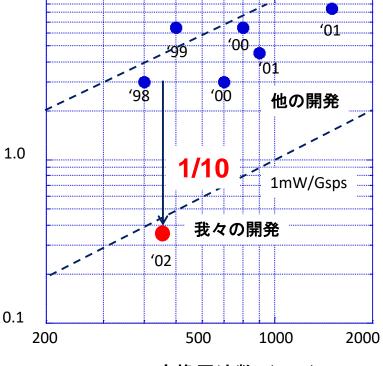

## 超高速CMOS ADCの開発

超高速ADCの民生機器応用にはCMOS化と低電力・低コスト化が不可欠

#### 91年当時、世界最高速の6b ADC バイポーラ技術

6b, 1GHz ADC 2W, 1.5µm Bipolar

A. Matsuzawa, ISSCC 1991

消費電力/2N

10.0

#### 当時、世界最高速のCMOS ADC

K. Sushihara and A. Matsuzawa, ISSCC 2000.

6b, 800MHz ADC 400mW, 2mm<sup>2</sup> 0.25µmCMOS

K. Sushihara and A. Matsuzawa, ISSCC 2002.

7b, 400MHz ADC 50mW, 0.3mm<sup>2</sup> 0.18μmCMOS

変換周波数(MHz)

Technology: 0.18um CMOS(3AL,1PS

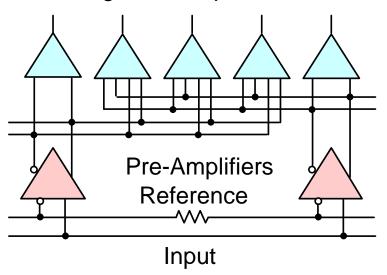

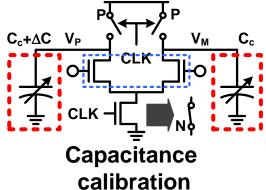

## ゲートで重みを付けた補間

CMOS フリップフロップ (F/F) のソースにリニア領域で動作するMOS TRを挿入で ゲートの重みにより補間が実現できる。F/Fは貫通電流が流れず、補間に 抵抗を用いないので、高速・低電力動作が可能。

$$G_{a} = \frac{\mu C_{ox}}{L} \left[ W_{1} \left( V_{i1p} - V_{T} \right) + W_{2} \left( V_{i2p} - V_{T} \right) \right]$$

$$G_{b} = \frac{\mu C_{ox}}{L} \left[ W_{1} \left( V_{i1n} - V_{T} \right) + W_{2} \left( V_{i2n} - V_{T} \right) \right]$$

Comparator latches with gate -weighted interpolation

K. Sushihara and A. Matsuzawa, ISSCC 2002.

$$G_{a} - G_{b} = \frac{\mu C_{ox}}{L} \left[ W_{1} \left( V_{i1p} - V_{i1n} \right) + W_{2} \left( V_{i2p} - V_{i2n} \right) \right]$$

$$W_{1} : W_{2} = \frac{m - k}{m} : \frac{k}{m} \quad k < m$$

$$V_{DD} \longrightarrow CLK$$

$$V_{i1p} \longrightarrow V_{i2p} \bigvee_{i2p} \bigvee_{i1n} \bigvee_{i2p} \bigvee_{i2p$$

Gate-weighted interpolation

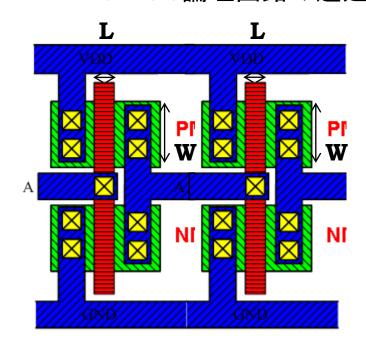

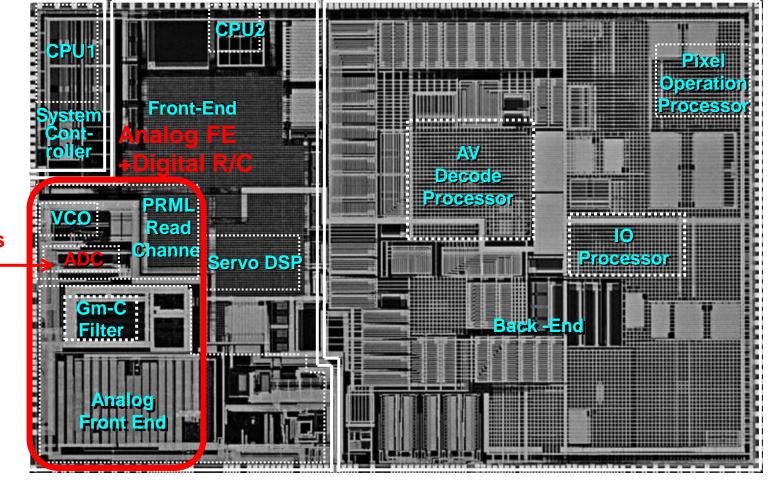

#### DVD 用完全ワンチップアナ・デジ混載SoCの実現/

#### DVDシステムを完全にワンチップ化した世界初のDVD用アナ・デジ混載Sioccolle

#### その後SoCによるシステムレベルの集積が進展

Okamoto,..., A. Matsuzawa., ISSCC 2003, JSC 2003. 0.13µm, Cu 6Layer, 24MTr

7b, 400MS/s

OADC —

Pursuing Excellence

#### アナログ・デジタル混載SoCの威力

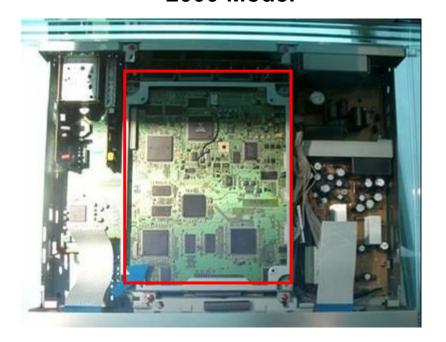

システム集積が可能なアナ・デジ混載SoCは、機器の高性能化、簡素化、低コスト化に大いに貢献した。また、DVDのノートPC搭載を可能にした。

SoC: System on a Chip (システムLSI)

'2000 Model DVD Recorderの例

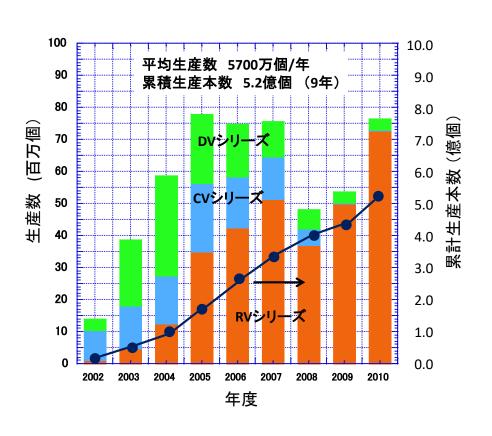

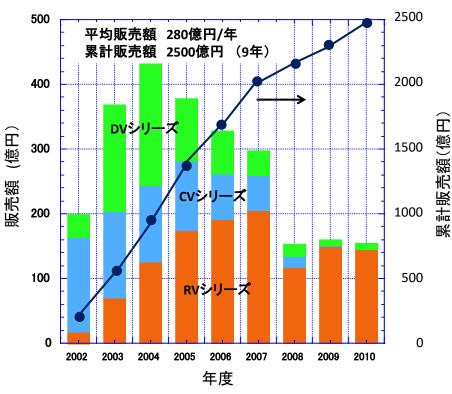

#### DVD用SoCの生産・販売

DVD用SoCは累積数量5.2億個,累積販売額2500億円に達した。

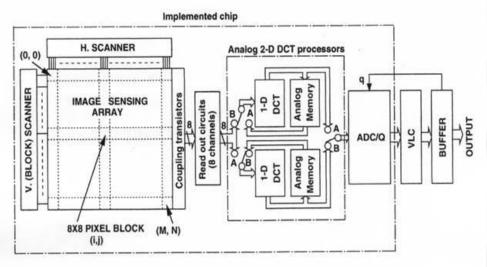

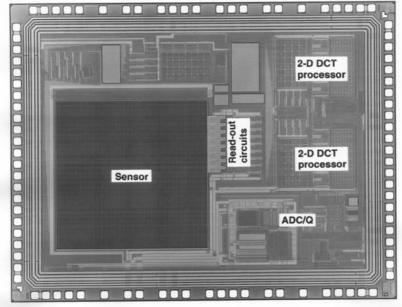

#### アナログDCT内蔵CMOSイメージセンサー

アナログDCTやADCの参照電圧コントロールによる可変量子化などのアナログ画像圧縮機能を内蔵しCMOSイメージセンサー。 信号処理機能を内蔵したCMOSイメージセンサーのパイオニア CMOSイメージセンサーの重要性と、CCDでは実現困難な機能が実現可能なことを喚起した。イメージャー分野のSoC化

#### 豊橋技科大(現 静岡大), 川人先生との共同開発

#### Kawahito, et al., ISSCC '97

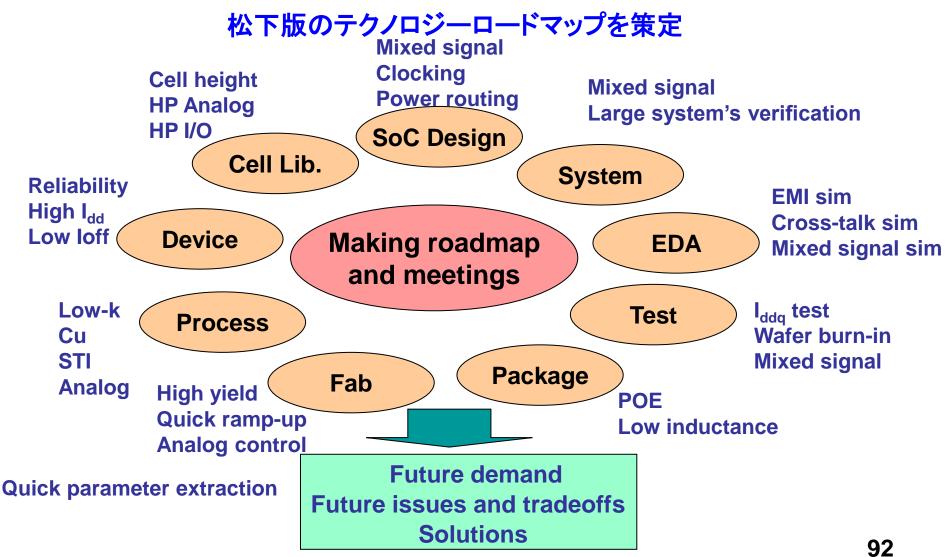

## システムLSI開発責任者として

1998年、45才で参事・GM(部長級)になった。それからの5年間はLSI技術開発のプロジェクトリーダーとしてだけではなく、松下のシステムLSI (SoC)を世界一にするために、設計技術だけでなく、次ページのように必要なことは全て行った。この結果、松下のアナ・デジ混載SoCは世界トップクラスになった。

#### Matsushita Electric Annual Report 1998

"The concept of a one-chip solution is now dominant in the semiconductor industry. Matsushita's system LSIs, which embody its expertise in finished products, underpin the speedy development of all compact, high-performance digital equipment."

#### Dr. Akira Matsuzawa

Chief R&D Manager, Advanced LSI Technology Development Center of Matsushita's Corporate Semiconductor Development Division, Japan

A decoder LSI for reproducing images in a digital satellite TV receiver

## SoC開発に向けた取り組み

- アナ・デジ混載チップの開発

- アナ・デジ混載SoC開発体制の確立

#### 当時取組んだこと

- アナログIP(ADC, DAC, PLL, Filter, 電源など)の開発

- デジタルIP(スタセル, SRAM, ROM, I/O)の開発と外部委託(Virage, Artisan)

- 設計・プロセス間の連携体制の確立

- デバイスパラメータ設定(基準, Spice抽出), 0.25μm, 0.18μm, 0.13μm

- アナ・デジ混載用EDAシステムの開発

- Cadenceなどとの共同開発

- Antrimへの出資(4億円), NeolinearやBarcelona deignとの協業

- 松下半導体内(+機器側)の全アナログ関係の統合設計技術の推進

- 国内外の大学との連携

- UCLA: Abidi教授とのBluetooth トランシーバの共同開発

- Stanford: エグゼクティブアドバイザー

- KU-Leuven: Gielen教授とのアナ・デジEDA技術の開発

- 国家プロジェクト(SOIを用いた自然エネルギで動作する機器の開発)

- アナログCMOS設計教育の企画と実施

- 外部Fab(TSMC)の選定と試作体制の確立

## システムLSI (SoC)の課題

SoCの開発期間は年々短縮が要求される反面、システムは複雑化し、開発費は高騰

ところが通常のアナログLSIは2~3回の再設計を必要とする。 このような状況はアナデジ混載SoCでは許されない。

#### 新たな開発戦略と設計システムを確立する必要があった

A. Matsuzawa, Invited speech, "How to Make Efficient Communication, Collaboration, and Optimization from System to Chip", IEEE 40th Design Automation Conference, pp. 26.2, 2003.

#### 多種の技術の結集とロードマップ策定

SoC開発には多くの技術の結集が必要であり、協調と協働を円滑にするではをxcellence まず、必要な技術とその時期を明確にしたロードマップ作成が不可欠である

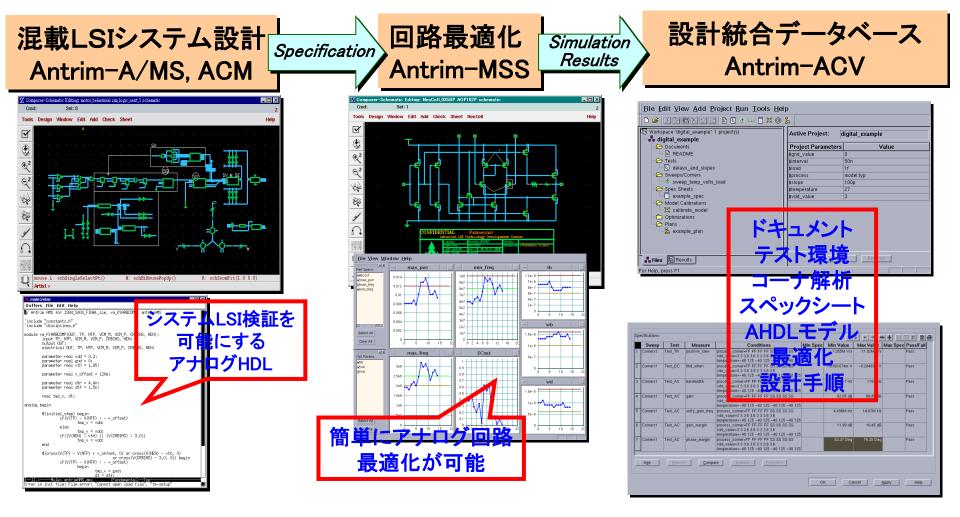

## アナ・デジ統合回路設計環境の開発

CadenceやAntrim(ベンチャー会社)と共同で設計環境を構築でExcellence

●回路設計工数比(x10~x50)

#### SoC時代のチップビジネス

- ファウンドリ・ファブレス化は必然

- 単一の商品群で工場全てを埋めるのは不可能 DVD用SoCは年間1億個を出荷したが、世界シェア100%としても 工場は埋まらない

- 大量に販売できる分野は、スマートフォン、PC、データセンタくらい

- ファブレスでも世界市場でトップクラスを取らないと収益は厳しい

- アナログ技術ベースのファブレスでもファウンドリを使うしかない

- ファウンドリは工場とは違う

- 設計に対する「サービス」の充実が死活的に重要

- PDK・Pcellの充実:バラツキ、ノイズ、RF特性、寄生素子などのアナログ対応

- モデルの正確さ, トランジスタの多様性, RFオプション

- EDAとの連携

- プロセス・デザインルールが多様化

- 製品ごとに最適なデザインルールがあり、多様化

# 95 TOKYO TECH Pursuing Excellence

#### 60GHz, ミリ波CMOSトランシーバの開発

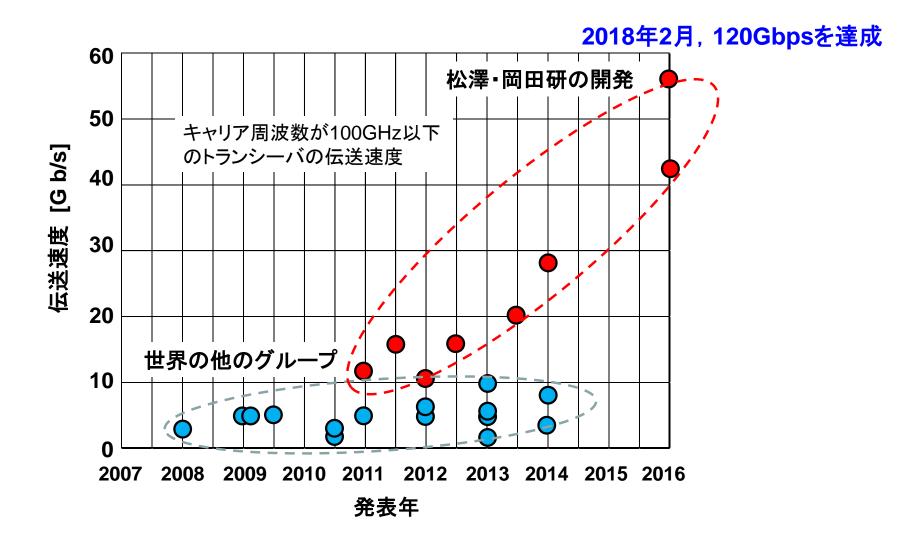

2003年,東工大着任後は総務省プロによるミリ波CMOSトランシーバーの開発に注力。難易度の高い研究開発であったが、開発に成功し、データ伝送速度で世界トップを連打。世界一の研究室に育てた。

ミリ波は5Gになって初めて本格使用されたが、この研究開発が 幾分かはミリ波通信の実用化に寄与していると思われる。

## 総務省ミリ波プロジェクト

#### • 概要

- 60GHz帯を中心とするミリ波通信を実現し、実用化を図るプロジェクト

- 東工大3研究室+ソニー・JRC・NEC・KDDI・Willcom・アムシスなどの 産学連携による大型プロジェクト

- 予算総額:6億円/年×(5年+4年)=54億円

#### • 松澤・岡田研の役割

プロジェクトリーダ:安藤教授

- 60GHz帯CMOSトランシーバーの高周波チップの開発

- 60GHz帯CMOSトランシーバーのアナログベースバンド回路の開発

- 40GHz帯. 中距離トランシーバのアナログベースバンド回路の開発

#### • プロジェクトの意味

- 予算規模・テーマともに研究室飛躍のきっかけ

- 技術的に超高難易度

- チップを動作させるにはベテランの技術者30人は必要

- 学生が開発し、実動作させるには高度のマネージメントが必要

- 開発に成功し、世界トップの研究室になった

## 2007年当時のミリ波トランシーバ

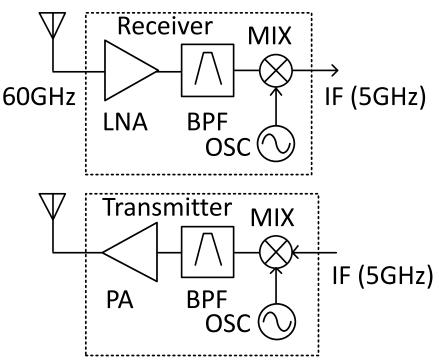

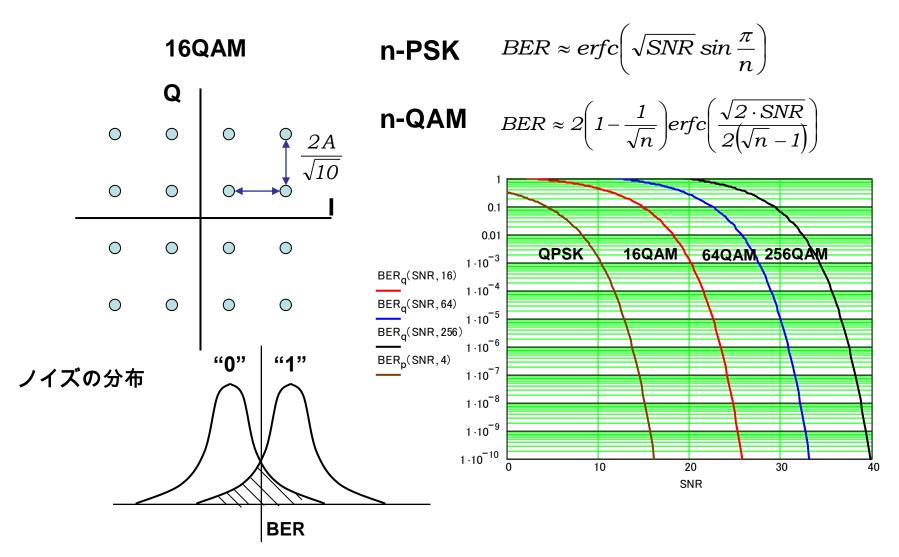

プロジェクト開始当時のミリ波トランシーバはGaAsなどの化合物半導体を用いたものであったが、伝送速度は実質50Mbpsと極めて低いものだった。ベースバンド回路が不十分であったのが主たる理由であるが、多値変調が使用できなかったからである。そこで高周波特性は劣るものの、将来のコストダウンと多値変調を実現する高度なベースバンド回路が可能なCMOS技術を用いて開発することを決めた。

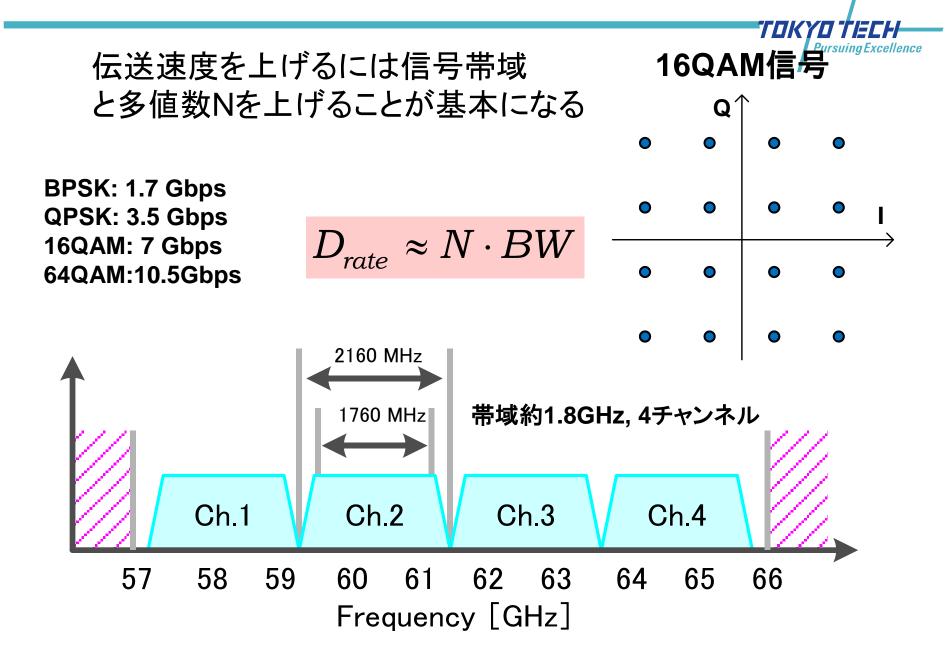

## 60GHz帯の超高速信号伝送

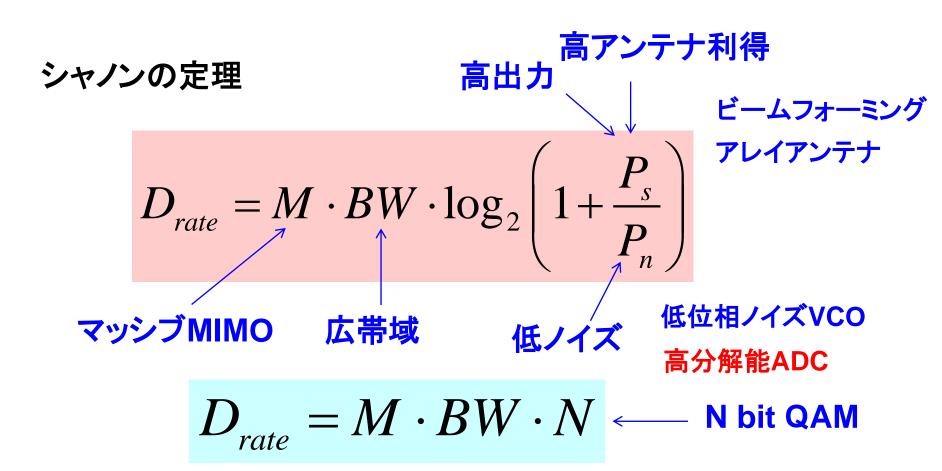

## データレート向上のシナリオ. Matsuzawa

データレート向上のためには高い周波数だけでなく 様々な性能の向上が必要。ADCの性能も効いてくる。

#### 無線システムにおける必要なSNR

低ビットレートの実現にはある程度のSNR(=分解能)が必要となる

Pursuing Excellence

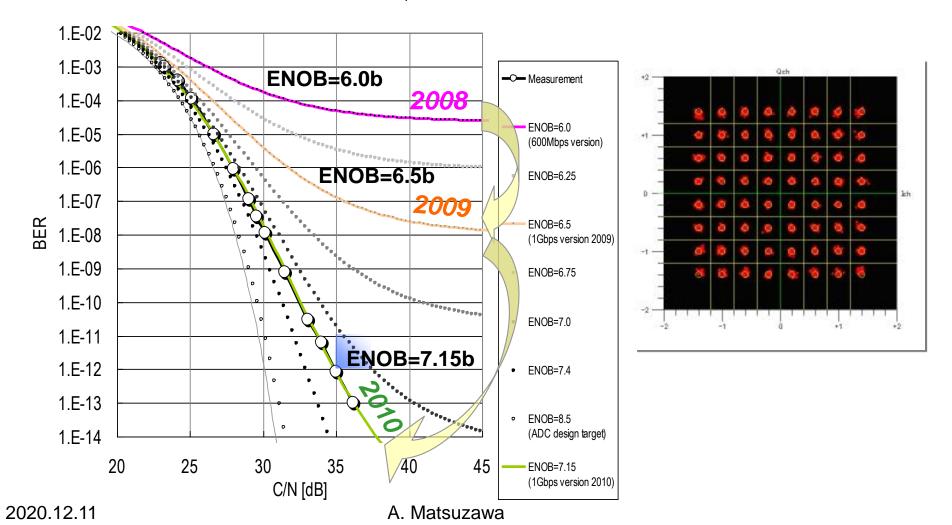

## 実例:40GHzミリ波基地局

#### 64QAM を通すためにはADCの性能向上が不可欠だった

C/N vs 64QAM\_BER on B-B pair

#### 松澤・岡田研が開発した60GHzトランシーバ集積回路

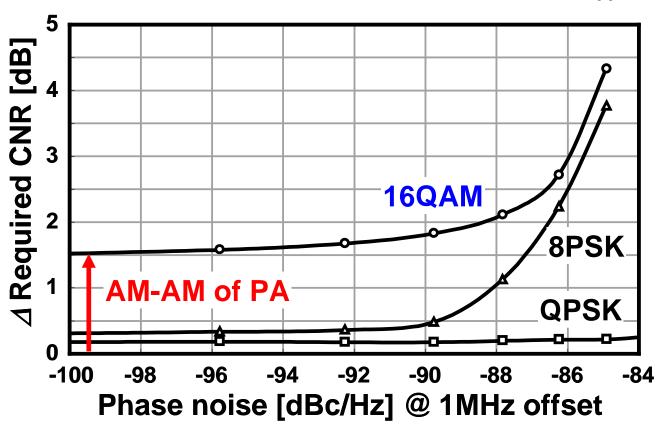

## 必要な直交発振器の位相ノイズ

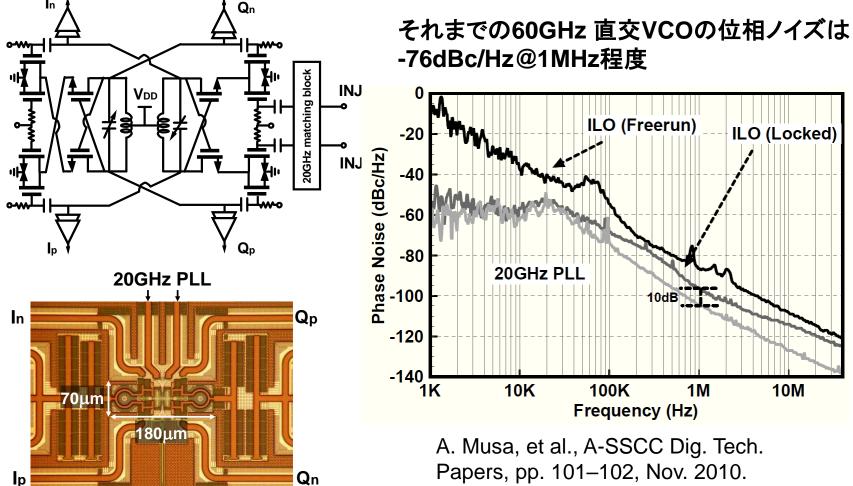

それまでの60GHz帯直交発振器は -76dBc/Hz@1MHz程度

K. Scheir, et al., ISSCC, pp. 494-495, Feb. 2009.

## コア技術:低位相ノイズ直交VCO

ダイレクトコンバージョンや16--64QAMが可能となった。

## 得られた伝送特性

#### 複素空間上の位相の揺らぎの抑制が重要

#### 世界初の64QAMを実現

| Channel/<br>Carrier<br>freq. | ch.1<br>58.32GHz                                          | ch.2<br>60.48GHz                                          | ch.3<br>62.64GHz                                          | ch.4<br>64.80GHz                                          | ch.1-ch.4<br>Channel bond                                              |

|------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|

| Modula-<br>tion              | 64QAM                                                     |                                                           |                                                           |                                                           | 16QAM                                                                  |

| Data rate*                   | 10.56Gb/s                                                 | 10.56Gb/s                                                 | 10.56Gb/s                                                 | 10.56Gb/s                                                 | 28.16Gb/s                                                              |

| Constella-<br>tion**         | ## # # # # # # # # # # # # # # # # # #                    |                                                           | # * * * * * * * * * * * * * * * * * * *                   |                                                           | 新香香香                                                                   |

| Spec-<br>trum**              | 0<br>-10<br>-20<br>-30<br>-40<br>-50<br>55.82 58.32 60.82 | 0<br>-10<br>-20<br>-30<br>-40<br>-50<br>57.98 60.48 62.98 | 0<br>-10<br>-20<br>-30<br>-40<br>-50<br>60.14 62.64 65.14 | 0<br>-10<br>-20<br>-30<br>-40<br>-50<br>62.30 64.80 67.30 | 0<br>-10<br>-20<br>-30<br>-40<br>-50<br>-55.56 58.56 61.56 64.56 67.56 |

| TX EVM**                     | -27.1dB                                                   | -27.5dB                                                   | -28.0dB                                                   | -28.8dB                                                   | -20.0dB                                                                |

| TX-to-RX<br>EVM***           | -24.6dB                                                   | -23.9dB                                                   | -24.4dB                                                   | -26.3dB                                                   | -17.2dB                                                                |

Pursuing Excellence

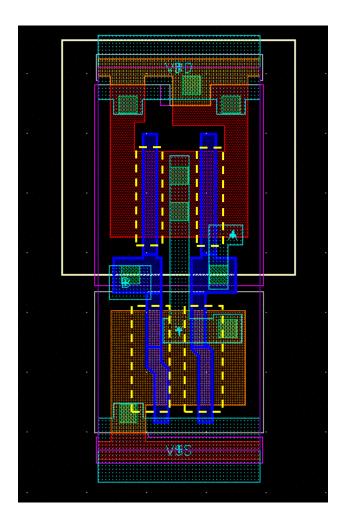

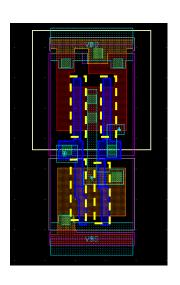

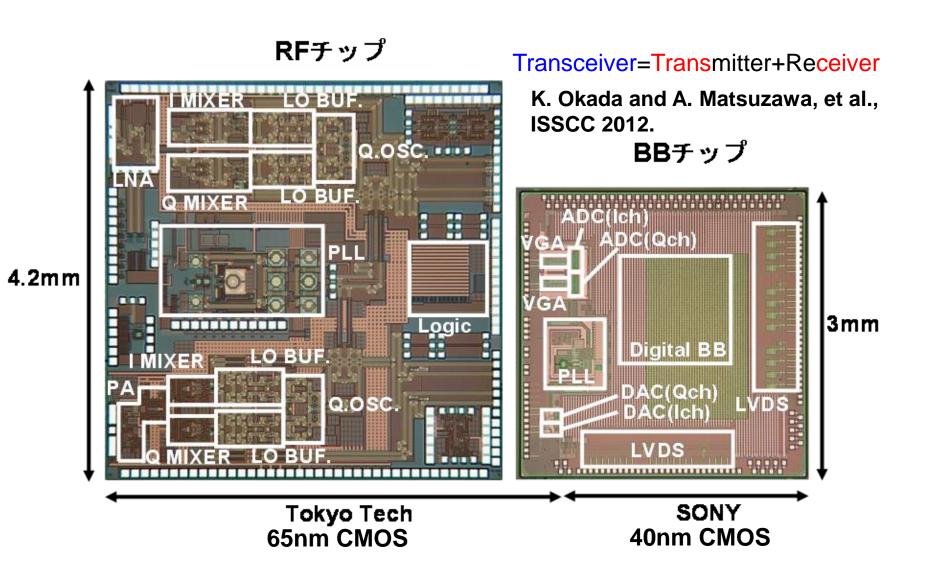

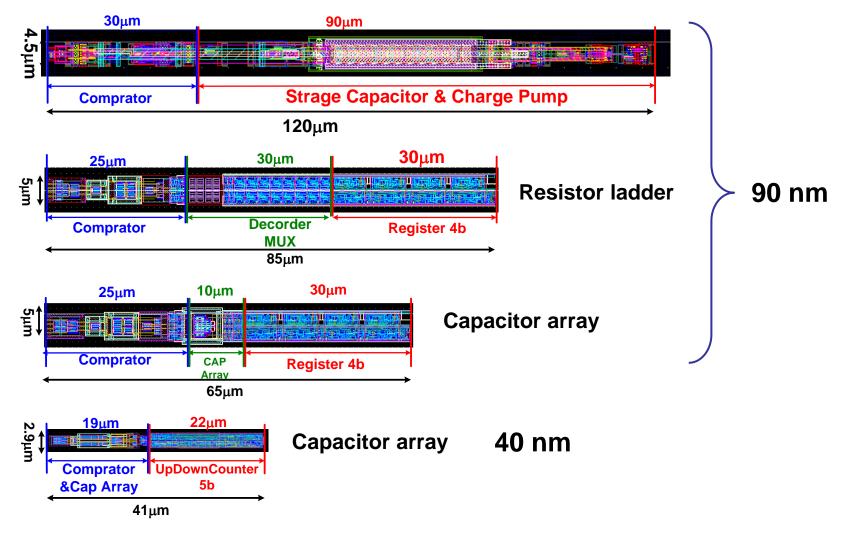

## 60GHz用に開発したSoC

## 開発した60GHz トランシーバ用40nm CMOS SoCには ADC, DAC, VGA, と PLLを集積した

RX: 300mW, TX: 110mW 40nm CMOS technology

3 mm Digital **RAM** RAM K. Okada and A. Matsuzawa, et al., ISSCC 2012.

ADC 5b, 2.3GSps, 12mW/ch

0.22 mm

2020.12.11

3 mm

A. Matsuzawa

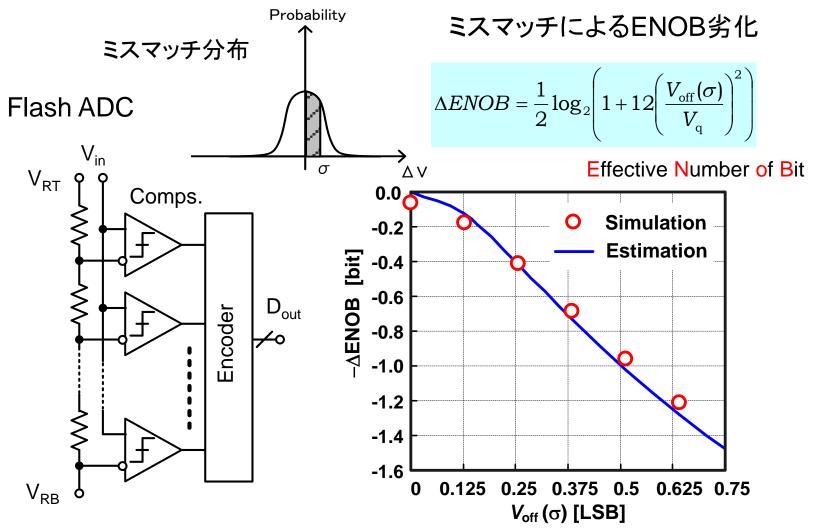

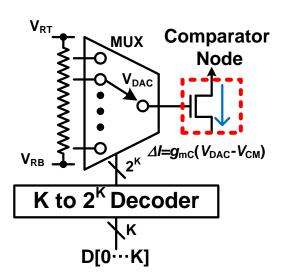

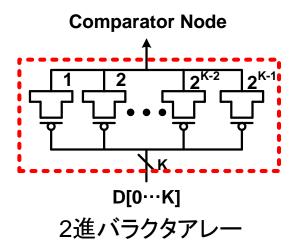

#### フラッシュADC設計

#### 比較器のミスマッチが実効分解能を決定する

2020.12.11 A. Matsuzawa

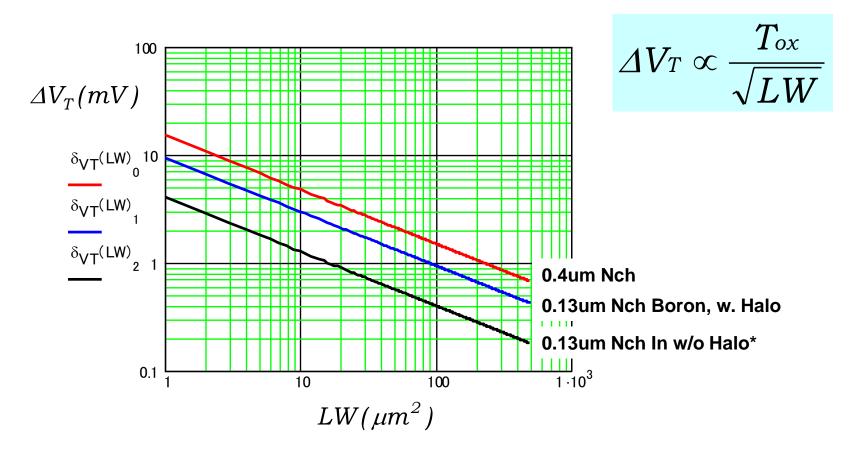

## V<sub>T</sub> ミスマッチ

V<sub>⊤</sub>ミスマッチを小さくするには大きなトランジスダサイズが必 微細化により,同一面積ではV<sub>⊤</sub>ミスマッチは減少する。

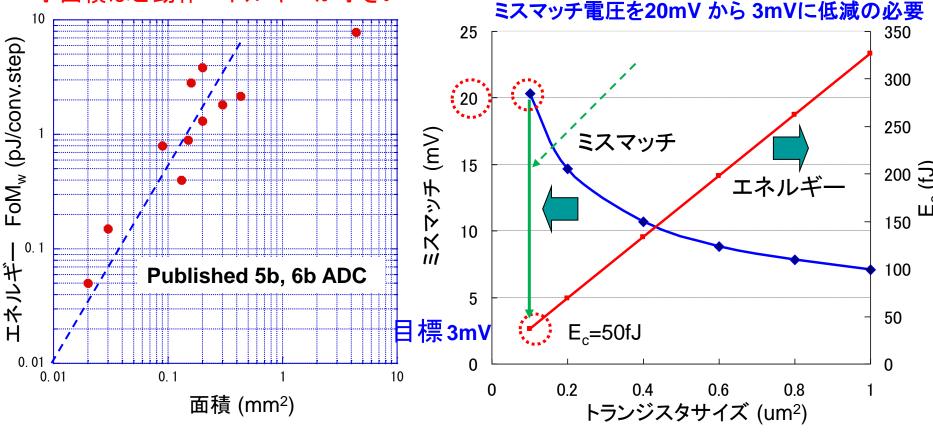

## 低エネルギーフラッシュADC開発戦略

小面積ほど動作エネルギーが小さいが、ミスマッチは増大**はまたけ**したがって、ミスマッチ補償技術が不可欠

$$FoM_{w} = \frac{P_{d} \cdot 2^{\Delta ENOB}}{f_{c} \cdot 2^{N}}$$

$$V_{

m offset}(\sigma) \propto rac{1}{\sqrt{LW}} ~~ E_c \propto C_c \propto LW$$

小面積トランジスタほどミスマッチが大きい

#### 小面積ほど動作エネルギーが小さい

2020.12.11

A. Matsuzawa

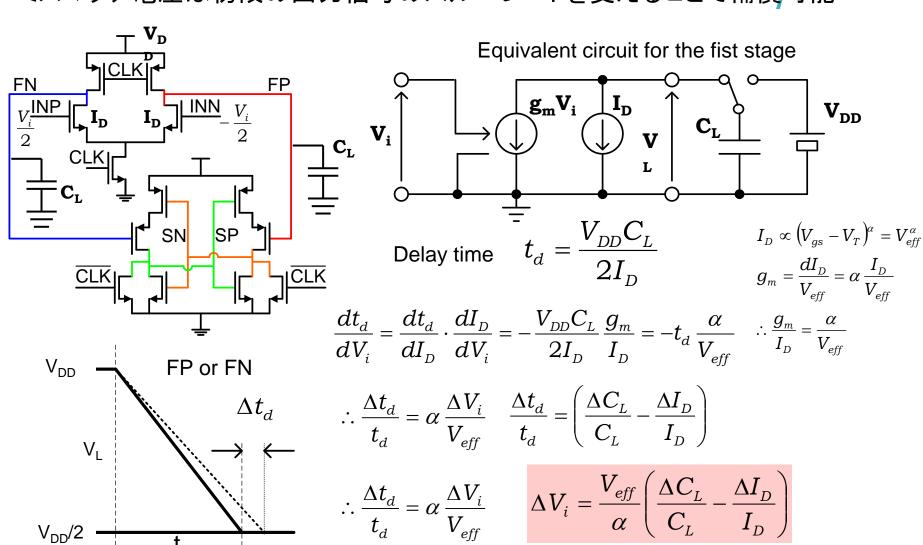

### ダイナミック比較器のミスマッチ電圧補償

ミスマッチ電圧は初段の出力信号のスルーレートを変えることで補償可能gExcellence

A. Matsuzawa

time

2020.12.11

Pursuing Excellence

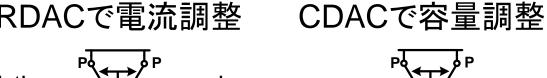

### ミスマッチ電圧のデジタル補償方法

#### RDACで電流調整

Y. Asada, K. Yoshihara, T. Urano, M. Miyahara and A. Matsuzawa,

"A 6bit, 7mW, 250fJ, 700MS/s Sub-ranging ADC" A-SSCC, pp. 141-144, Nov. 2009.

TOKYO TECH

### デジタルミスマッチ補償回路を搭載した比較器

CDAC方式が面積が小さい。補償回路はスケーリングで小さくできる

2020.12.11 A. Matsuzawa

**Pursuing Excellence**

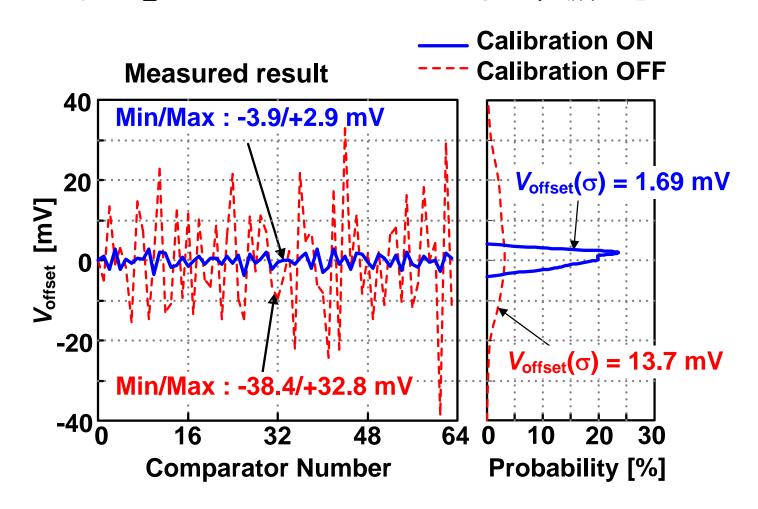

### デジタルミスマッチ補償の効果

ミスマッチ電圧は14mV から 1.7mVまで低減できた

M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, "A Low-Noise Self-Calibrating Dynamic Comparator for High-Speed ADCs," A-SSCC, Nov. 2008.

2020.12.11 A. Matsuzawa

# 60GHz 帯の伝送速度の進歩

松澤・岡田研究室では無線データ伝送速度の世界記録を更新

TOKYO TECH

**Pursuing Excellence**

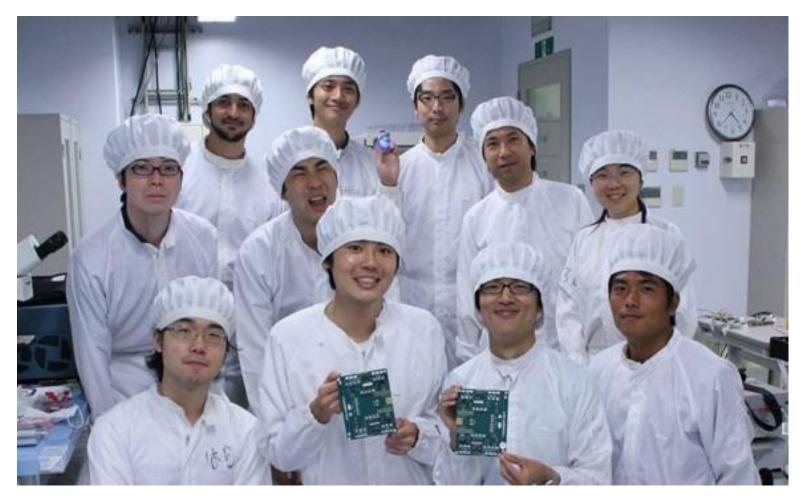

### ミリ波トランシーバの開発メンバー

学部4年生から博士課程学生までのチーム

団体戦と個人戦の組み合わせが重要

### ミリ波送受信デモ

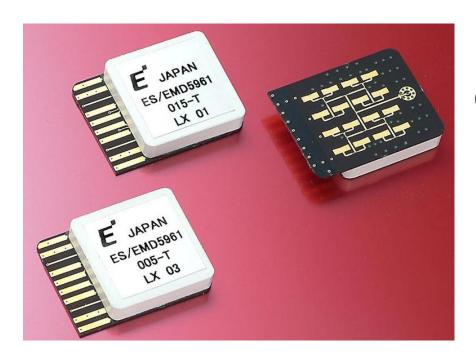

とても小さなパッケージにミリ波トランシーバが入っている。

実用レベルで世界最高速 毎秒 6.1Gビットのデータ伝送を達成

ミリ波の実用化に幾分かは貢献

超高速伝送実験のデモをお見せします

2016年3月2日 東工大 本館前

TRX

ゲート

http://www.titech.ac.jp/news/2016/033575.html

### TOKYO TECH Pursuing Excellence

# 教育活動

教育に関しては松下時代,東工大時代を通じて熱心に取り組んだ方だと思う。 自分が獲得したものはできるだけ皆に伝えていきたいと考えている。 学びながら教え,教えながら学んできた。

松下時代の講義の様子

# 松下電器時代の教育活動

TOKYO TECH Pursuing Excellence

ADCやアナログCMOSのパイオニアとして、社内外の教育活動を行った。

#### CDROMのビデオ教材

#### デジタル信号処理技術(社内研修講師)

- 年2回程度: ADC, DACの部分を担当

- 33才~40才まで担当

#### ・ ADC, DACに関する社外の研修講師

- 年2回程度,対象は他社の技術者

- 日本でADC開発を行う技術者はたいてい受講している

#### ・ 大学の非常勤講師(集中講義)

- 阪大,東北大,豊橋技科大

- VDECのセミナー

#### ・ 半導体グループのアナログCMOS回路設計教育

- 年間12テーマを設定し、分担

- 一部をシステムLSI学院がビデオ教材化し、外販

河崎さんのシステムLSI技術学院で、 撮影、編集、販売。 SONYでは400人くらいの技術者が 利用したと聞いている。

**Pursuing Excellence**

### デバイス開発研時代のメンバー'93~'96

アナログ, アナ・デジ, ローパワー関係の開発を担当

メンバーで手分けして,アナログCMOS設計のテキスト・CDROMを作成

# 東工大で始めた技術者教育

2004年~2012年まで日本情報技術センターでアナログCMOS技術を中心をできまする技術セミナーを開催。1000名程度の技術者が受講した。このセミナーは5回シリーズに縮小し、STARCでのセミナーに引き継がれる

- 電子回路設計とアナログ・デジタル信号処理の基礎

- 土曜日の空いた教室を

CMOSデバイス

利用して, 受講料を下げた

- アナログCMOS回路とOPアンプ設計の基礎

- CMOS ADC/DACの基礎

- パイプライン型CMOS ADC設計

- シミュレータを用いたアナログCMOS回路設計1

- アクティブCMOSフィルター設計

- ΣΔADC, DAC設計

- PLL設計

- RFCMOS回路設計 1 (ワイアレスシステムとその基礎)

- RFCMOS 設計 2 (基本RF-CMOS回路)

- 回路・システムシミュレーション技術

- アナ・デジ混載LSI設計とデジタルアシスト技術

- シミュレータを用いたアナログCMOS回路設計2

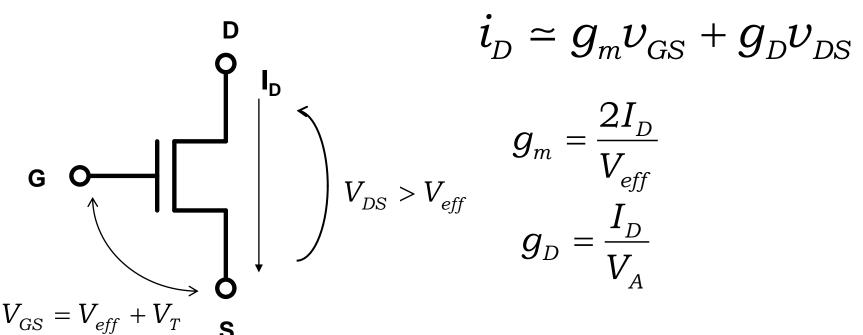

### アナログCMOS回路設計法の開発

私のアナログCMOS回路設計法の最大の特徴は、それまで多くのパラ $y^{Pursuign Excellenc}$ が必要であった、 $g_m$ ,  $g_D$ の計算をドレイン電流 $I_D$ , 有効ゲート電圧 $V_{eff}$ , アーリー電圧 $V_A$ だけを用いることで簡単にできるようにしたことである。

V<sub>eff</sub>, V<sub>A</sub>は最初にトランジスタの特性抽出さえしておけば, あとは簡単に計算できる。 実践的な設計経験と学問的洞察から生まれたものである。

#### MOSトランジスタ

TOKYO TECH

**Pursuing Excellence**

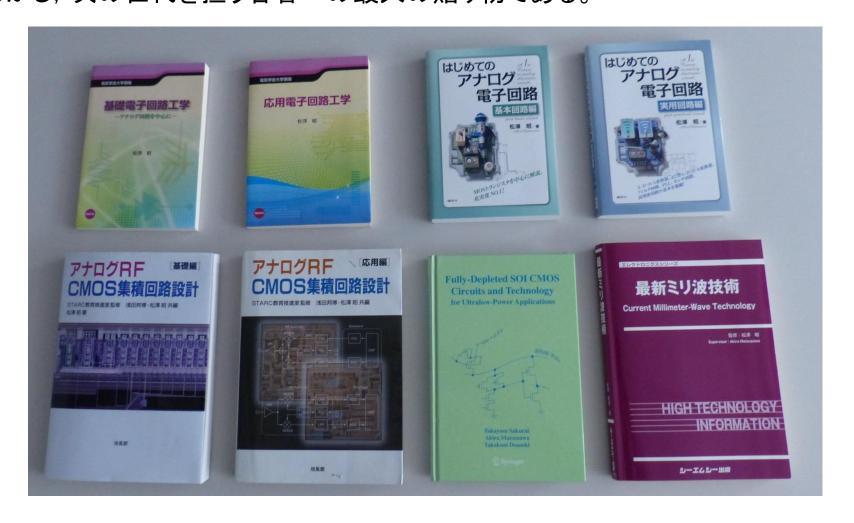

# 書籍の出版

書籍(テキスト)の執筆は時間がかかる作業で、休日のかなりの時間を費やした。しかし、次の世代を担う若者への最大の贈り物である。

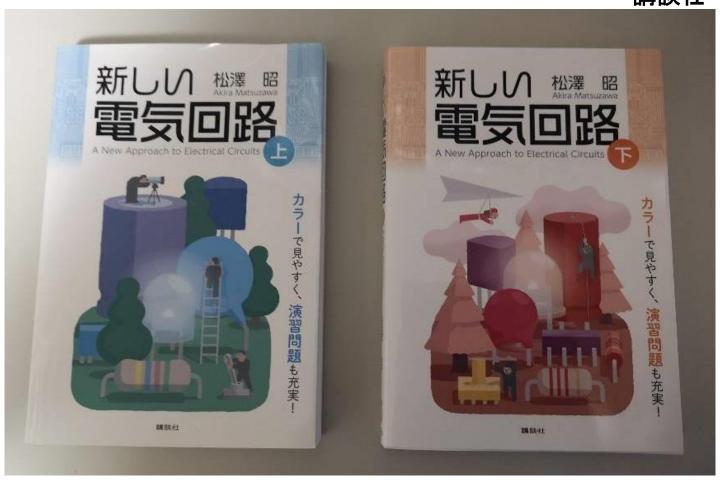

# 最近出版したテキスト

東工大、電気電子系の教育改革で、授業内容を見直した。 基幹科目である「電気回路」のための新しいテキストを出版。

講談社

# 授業

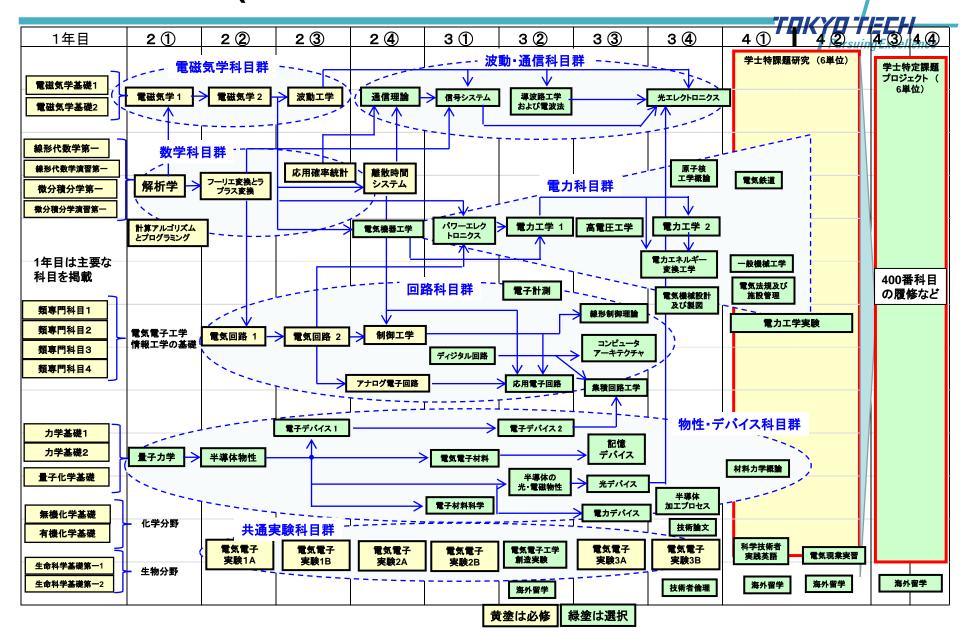

青字は新設授業

### 電気電子系の教育改革

### TOKYO TECH

#### 東工大電気電子系の教育改革の方向性を日経エレに発表

# 学生を「最強の技術者」に東工大が挑む教育改革

松澤 昭 東京工業大学大学院課工学研究科電子物理工学事項

「世界最高レベルの理工系総合大学」の実現を目指して 2016年度の開始をめどに教育改革を進める東京工業大学。 その一環として同校の電気系学科は カリキュラムや教育法を大胆に変えようとしている。 自動車や医療、建築、農業など多くの産業で電気系人材への需要が高まる 動きを受け、第一線で活躍できる技術者の育成を最優先する。 同校の松澤教授に改革の狙いと概要を解説してもらった。(本誌)

日経エレクトロニクス 2014年8月18日号

# 電気電子系の教育改革

- ・ 現状課題の把握

- 30名程度の学生への教育課題の聞き取り調査

- 必修20科目のテキストや教授資料を自ら分析

- 複数教員でのレビュー:授業内容,配布資料,レポート

- 授業参観の実施

- 電気電子系の教育改革の実施

- 基盤的知識の明確化と体系化とカリキュラムチャートの作成

- 科目データベースの構築

- 科目概要の作成

- シミュレータ活用の推進

- MATLABの無料化へのプッシュ

- MathWorks社から支援の取り付け

- MATLAB普及のためのセミナー開催とTAの活用

- 電気系科学技術懇話会の設立

- 年間7回程度:教員が学生や他の先生方に専門分野を分かりやすく伝える

- 電気系若手教員FDの会の設立

### 理工系特有の取組み:シミュレータの活用 127

理工系教育の革新において、シミュレーション プラットフォームは極めて重要である。

東工大では27年度から全ての教職員、全ての学生がフリーで世界標準の科学技術計算ツールのMATLAB® を利用できるようになった。

#### 取組み

- ・2名のTAによる技術サポート

- ・教員・学生向けのセミナー開催

- ・授業・実験での使用のサポート

#### ねらい

- ・理論の可視化による理解の促進

- ハードウエアとのリンクによる実験

- ・学生のプログラミング技術の向上

- ・意欲のある学生は自ら、プログラミングしシステムを構築

意欲的な学生をどんどん伸ばす仕組が必要

#### 電磁波の様子(理論の可視化)

世界で5000校以上の大学で採用

### 電気電子系(学部)のカリキュラム体系の構築

# 全体のまとめ

#### • TV-ビデオ機器のデジタル化

- TV・ビデオ機器のデジタル化は日本が主導し、HDTV、DVD、ハンディーカムなどのデジタルTV・ビデオ機器を創出した

- ビデオ用ADCはそれを実現するキーコンポーネントであり、日本メーカーが開発を主導した

#### ADC開発

- ADCは新規システムにとって絶えずボトルネック

- デジタル機器用ではあるが高度なアナログ技術がベース

- デバイスと機器の仕様により最適なアーキテクチャが異なる

- デバイスの欠点を克服し、利点を最大限生かす回路技術

- 結局ロジックと同じでスケーリング則が適用できるアーキが残った

#### 懸念事項

- ADCやRFなどの高度アナログ技術は海外メーカーに依存

- 国内の開発力, 開発人材が枯渇

# 集積回路設計40年を振り返って

### 集積回路設計を楽しみながら幾分かは社会に貢献できたと思う

ADCは未だにシステムのボトルネック, 息の長い開発になった 幾分の独創性を発揮したが, 時代の要請に必死で応えただけかも

- TV-ビデオのデジタル化の時代に遭遇

- 集積回路の1つの歴史を体現

- ボード→バイポーラ→ Bi-CMOS→ CMOS→ SoC

- ビデオADCの開発で画期的な高性能・低電力,技術を牽引

- 各種補間技術の開発:抵抗補間,容量補間,ゲート補間

- ミリ波利用に貢献したミリ波CMOSトランシーバーの開発

- 教育は国の根幹, 学生・技術者教育に最大限努力

- 学会で楽しみ,運営に貢献

- 事業に関してもそれなりに応えてきたつもり

# 今後の半導体・集積回路開発

- ・ 機器・システムの開発が最重要

- 半導体は最終製品ではない、機器・システムが伸びなければ半導体も伸びない。機器・システムが必要であれば、半導体技術開発は困難であっても行われる

- 三次元積層:フラッシュメモリ

- 裏面照射・張り合わせ: CMOSイメージセンサ

- アンテナ・チップ実装:5Gシステム

- 日本が開発のリーダシップを取れる分野を強くする

- 次世代車技術(EV, ADAS, CASE, etc.)

- 光·電気融合技術(IOWN)

- ポスト5G, 6G技術(光通信, ミリ波・テラヘルツ通信)

- その他?

TOKYD TECH-Pursuing Excellence

# 終わり